का मुख्य दोष है दहनशील सर्किट यह वर्तमान और पिछले राज्यों को बचाने के लिए किसी भी मेमोरी का उपयोग नहीं करता है। इसलिए इनपुट की पिछली स्थिति का सर्किट की वर्तमान स्थिति पर कोई प्रभाव नहीं पड़ता है। जबकि, अनुक्रमिक सर्किट में मेमोरी होती है, इसलिए आउटपुट इनपुट के आधार पर भिन्न हो सकते हैं। इस प्रकार के सर्किट पिछले इनपुट, आउटपुट, क्लॉक और एक मेमोरी तत्व का उपयोग करते हैं। यहां मेमोरी एलिमेंट्स लैच या फ्लिप-फ्लॉप हो सकते हैं। अनुक्रमिक सर्किट को विभिन्न तरीकों से डिज़ाइन किया गया है जैसे कि ROM और फ़्लिप, PLAs का उपयोग करके, CPLD (कॉम्प्लेक्स प्रोग्रामेबल लॉजिक डिवाइस) , FPGAs (फील्ड प्रोग्राम गेट ऐरे) । इस लेख में, हम केवल PLAs का उपयोग करके अनुक्रमिक सर्किट को डिज़ाइन करने के तरीके पर चर्चा करने जा रहे हैं।

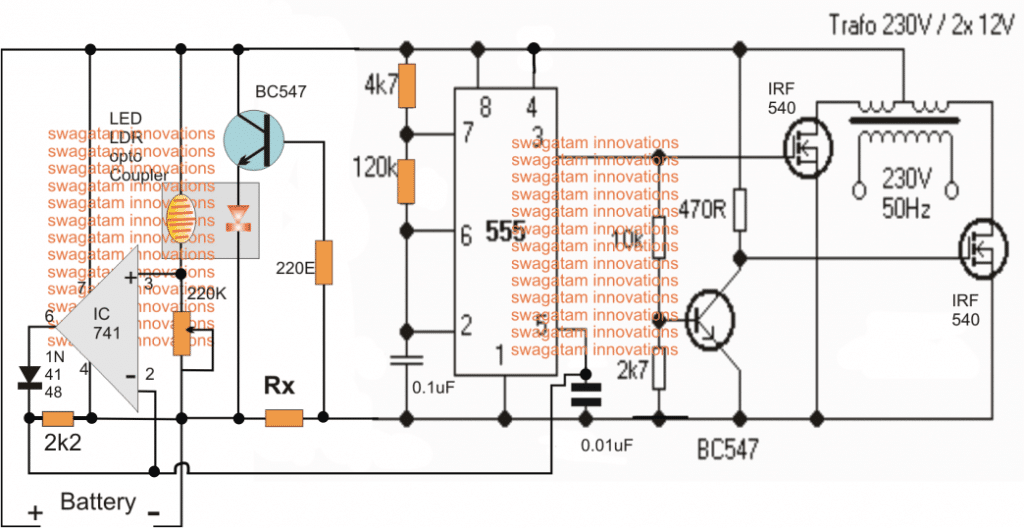

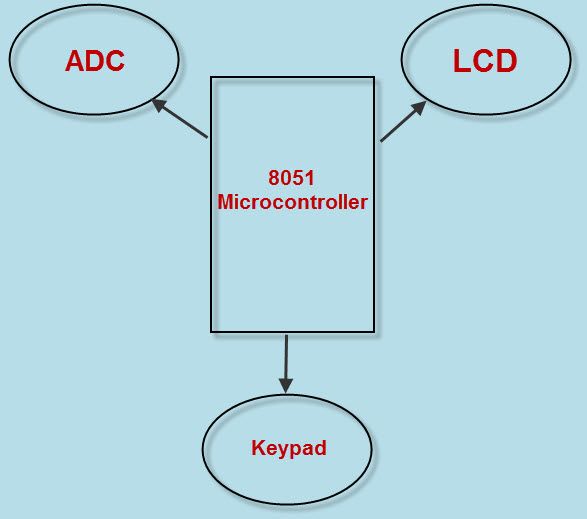

नीचे दिखाए अनुसार अनुक्रमिक सर्किट का ब्लॉक आरेख:

अनुक्रमिक सर्किट के ब्लॉक आरेख

पीएलए का उपयोग करके अनुक्रमिक सर्किट का डिजाइन

अनुक्रमिक सर्किट PLAs (प्रोग्रामेबल तर्क Arrays) और फ्लिप-फ्लॉप का उपयोग करके महसूस किया जा सकता है। इस डिजाइन में, राज्य असाइनमेंट महत्वपूर्ण हो सकता है क्योंकि एक अच्छा राज्य असाइनमेंट का उपयोग उत्पाद की शर्तों की आवश्यक संख्या को कम कर सकता है और इसलिए पीएलए के आवश्यक आकार को कम कर सकता है। एक उत्पाद शब्द को शाब्दिक अर्थ के रूप में परिभाषित किया गया है, जहां प्रत्येक शाब्दिक या तो एक चर है या इसकी उपेक्षा है।

आइए हम डिज़ाइन को एक कोड कनवर्टर मानते हैं। नीचे दी गई राज्य तालिका में एक पीएलए और तीन का उपयोग करके महसूस किया जा सकता है फ्लिप फ्लॉप जैसा कि नीचे दिखाया गया है। यह सर्किट कॉन्फ़िगरेशन ROM फ्लिप-फ्लॉप आधारित डिज़ाइन के समान है, सिवाय इसके कि ROM को उपयुक्त आकार के PLA द्वारा प्रतिस्थापित किया जाए। राज्य असाइनमेंट नीचे दी गई सत्य तालिका की ओर जाता है। इस तालिका को चार इनपुट, 13 उत्पाद शर्तों और चार आउटपुट के साथ एक PLA में संग्रहीत किया जा सकता है, लेकिन यह 16-शब्द रोम की तुलना में आकार में बहुत कम की पेशकश करेगा।

| X Q1 Q2 Q3 | डी 1 डी 2 डी 3 के साथ |

| ० ० ० ० ० ० ० १ ० ० १ १ ० ० ० १ १ ० १ ० ० ० १ ० १ 0 1 1 0 0 1 1 1 १ ० ० ० १ ० ० १ १ ० १ १ ० 1 0 1 1 १ १ ० ० १ १ ० १ १ १ १ १ १ ० १ १ १ १ १ | १ ० ० १ 1 0 1 1 ० १ ० ० ० १ ० १ १ १ ० १ १ ० ० ० ० १ ० ० ० एक्स एक्स एक्स एक्स ० ० १ १ ० ० १ ० ० १ १ ० ० १ १ ० १ १ 0 1 1 0 १ ० ० ० एक्स एक्स एक्स एक्स एक्स एक्स एक्स एक्स |

टेबल: ट्रुथ टेबल

वर्तमान राज्य

| अगला स्टेट एक्स = 0 1 | वर्तमान OUTPUT (Z) |

| सेवा मेरे | बी सी | १ ० |

ख सी | डे और ई | १ ० ० १ |

घ है | ज ज एच एम | ० १ १ ० |

एच म | ए ए सेवा मेरे - | ० १ 1 - |

टेबल: स्टेट टेबल

पीएलए का उपयोग करते हुए अनुक्रमिक सर्किट का डिजाइन

इनपुट आउटपुट समीकरण कर्णघट मैप द्वारा व्युत्पन्न

यहां, जैसा कि सात राज्य हैं, तीन डी फ्लिप-फ्लॉप की आवश्यकता है। इस प्रकार, 4 इनपुट और 4 आउटपुट के साथ एक पीएलए सर्किट की आवश्यकता होती है। यदि कोड कनवर्टर के राज्य असाइनमेंट पर विचार किया जाता है, तो परिणामी आउटपुट समीकरण और D फ्लिप-फ्लॉप इनपुट समीकरणों को कर्णघ से प्राप्त किया जा सकता है, जिसे निम्नलिखित समीकरण लिखा जा सकता है

D1 = Q1 + = Q2 ”

D2 = Q2 + = Q2 ”

D3 = Q3 + = Q1 Q2 Q3 = X 'Q1 Q3' = X Q1 'Q2'

Z = X 'Q3' + X Q3

| X Q1 Q2 Q3 | डी 1 डी 2 डी 3 के साथ |

- - 0 - - 1 - - - १ १ १ ० १ - ० 1 0 0 - ० - - ० ग्यारह

| ० १ ० ० ० ० १ १ ० ० ० ० १ ० ० ० १ ० ० ० १ १ ० ० ० १ ० ० ०

|

पीएलए तालिका जो इन समीकरणों से मेल खाती है, ऊपर दी गई तालिका में दी गई है। चार इनपुट, सात उत्पाद शर्तों और चार आउटपुट के साथ पीएलए का उपयोग करके इस तालिका को महसूस किया जा सकता है। शुरू में उपरोक्त डिजाइन के संचालन को सत्यापित करने के लिए, मान लें कि X = 0 और Q1Q2Q3 = 000। यह तालिका में पंक्तियों - - 0- और 0 - - -0 का चयन करता है, इसलिए Z = 0 और D1D2D3 = 100। सक्रिय घड़ी बढ़त के बाद, Q1Q2Q3 = 100। यदि अगला इनपुट X = 1 है, तो पंक्तियाँ - - 0 - और - 1- चयनित हैं, इसलिए Z = 0 और D1D2D3 = 110। सक्रिय घड़ी बढ़त के बाद, Q1Q2Q3 = 110।

प्रोग्रामेबल तर्क सरणी (पीएलए)

प्रोग्रामेबल लॉजिक एरे एक प्रोग्रामेबल लॉजिकल डिवाइस है। यह आमतौर पर कॉम्बिनेशन लॉजिक सर्किट को लागू करने के लिए उपयोग किया जाता है। PLA में प्रोग्रामेबल और प्लेन (AND array) का एक सेट होता है, जो प्रोग्रामेबल OR प्लेन (OR array) के एक सेट से लिंक होता है, जो तब आउटपुट प्रोड्यूस करने के लिए प्रोविजनलली कॉम्प्लीमेंट किया जा सकता है। यह लेआउट बड़ी संख्या में लॉजिक फ़ंक्शंस को संश्लेषित करने की अनुमति देता है उत्पादों का योग (SOP) विहित रूप। पीएलए का एक सरल ब्लॉक आरेख नीचे दिया गया है।

एक PLA के ब्लॉक आरेख

पीएलए और पाल के बीच मुख्य अंतर (प्रोग्राम करने योग्य सरणी तर्क) है,

PLA: दोनों और विमान और OR विमान प्रोग्राम करने योग्य हैं।

पाल: ओनली एंड प्लेन प्रोग्रामेबल है, जबकि ओआर प्लेन तय है।

पीएलए की बेहतर समझ के लिए, यहां हम नीचे दिए गए उदाहरण पर विचार कर रहे हैं।

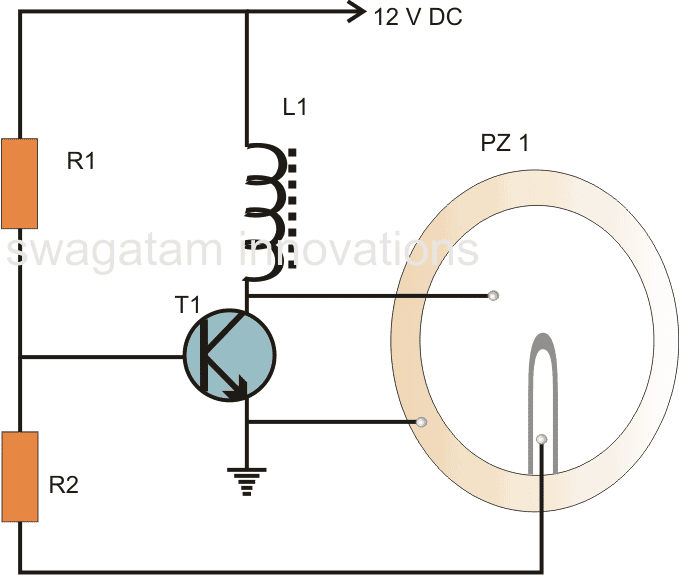

आइए इन फ़ंक्शन को एफ 1 और एफ 2 को लागू करने का प्रयास करें

इनपुट्स X1, x2, x3 और उनके संबंधित पूरक सिग्नल प्रोग्रामेबल और प्लेन को दिए गए हैं, वहां हमें P1, P2, P3called minterms के रूप में और प्लेन आउटपुट मिलेंगे। फिर इन संकेतों को प्रोग्रामेबल या प्लेन को आवश्यक आउटपुट फंक्शन f1 और f2 (उत्पादों की राशि) का उत्पादन करने के लिए दिया जाता है। नीचे दिए गए आंकड़े में पीएलए के कार्यान्वयन के लिए गेट स्तर के कार्यान्वयन का वर्णन है।

पीएलए का कार्यान्वयन

यह सब पीएलए के उपयोग से अनुक्रमिक सर्किटों के डिजाइनिंग के बारे में है। हम मानते हैं कि इस आलेख में दी गई जानकारी आपके लिए इस अवधारणा की बेहतर समझ के लिए सहायक है। इसके अलावा, इस लेख या किसी भी मदद के बारे में कोई प्रश्न विद्युत और इलेक्ट्रॉनिक्स परियोजनाओं को लागू करना , आप नीचे टिप्पणी अनुभाग में टिप्पणी करके हमें संपर्क कर सकते हैं। यहाँ आपके लिए एक सवाल है, अनुक्रमिक सर्किट से क्या अभिप्राय है?