विभिन्न प्रकार के लॉजिक परिवार उपलब्ध हैं जिनका उपयोग डिजिटल लॉजिक सर्किट को डिजाइन करने में किया जाता है; रेसिस्टर ट्रांजिस्टर लॉजिक (आरटीएल), एमिटर कपल्ड लॉजिक (ईसीएल), डायोड ट्रांजिस्टर लॉजिक (डीटीएल), कॉम्प्लीमेंट्री मेटल ऑक्साइड सेमीकंडक्टर लॉजिक (सीएमओएस), और ट्रांजिस्टर-ट्रांजिस्टर लॉजिक (टीटीएल) . इन तर्क परिवारों में से, डीटीएल तर्क परिवार का उपयोग आमतौर पर 1960 और 1970 के दशक से पहले अधिक उन्नत तर्क परिवारों को बदलने के लिए किया जाता था जैसे सीएमओएस और टीटीएल. डायोड-ट्रांजिस्टर लॉजिक का एक वर्ग है डिजिटल सर्किट इसे डायोड और ट्रांजिस्टर के साथ डिज़ाइन किया गया है। इसलिए डायोड और ट्रांजिस्टर का संयोजन काफी छोटे घटकों के साथ जटिल तर्क कार्य करने की अनुमति देता है। यह आलेख संक्षिप्त जानकारी प्रदान करता है डीटीएल या डायोड ट्रांजिस्टर तर्क और इसके अनुप्रयोग.

डायोड ट्रांजिस्टर लॉजिक क्या है?

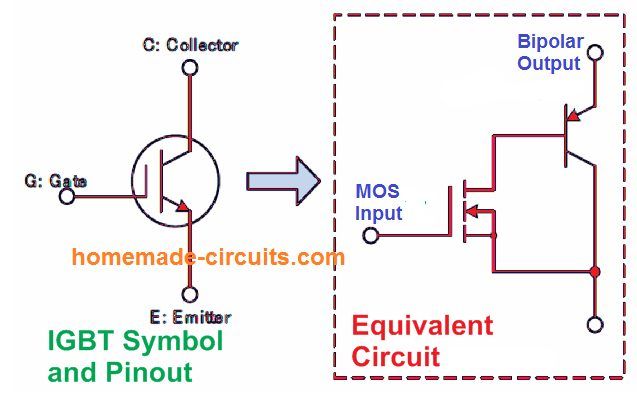

डायोड ट्रांजिस्टर लॉजिक एक लॉजिक सर्किट है जो डिजिटल लॉजिक परिवार से संबंधित है जिसका उपयोग डिजिटल सर्किट बनाने के लिए किया जाता है। इस सर्किट को डिज़ाइन किया जा सकता है डायोड और ट्रांजिस्टर जहां इनपुट पक्ष पर डायोड का उपयोग किया जाता है और आउटपुट पक्ष पर ट्रांजिस्टर का उपयोग किया जाता है, इस प्रकार इसे डीटीएल के रूप में जाना जाता है। डीटीएल सर्किट का एक विशिष्ट वर्ग है जिसका उपयोग विद्युत संकेतों को संसाधित करने के लिए वर्तमान डिजिटल इलेक्ट्रॉनिक्स में किया जाता है।

इस लॉजिक सर्किट में, डायोड लॉजिक कार्यों को करने में उपयोगी होते हैं, जबकि ट्रांजिस्टर का उपयोग प्रवर्धन कार्यों को करने के लिए किया जाता है। की तुलना में डीटीएल के कई फायदे हैं अवरोध ट्रांजिस्टर तर्क जैसे; उच्च फैन-आउट मान और उच्च शोर मार्जिन के कारण, DTL को RTL परिवार से बदल दिया गया है। डायोड ट्रांजिस्टर लॉजिक की विशेषताएं मुख्य रूप से शामिल हैं; डिजिटल संस्कृतिहीन, डिजिटल रणनीतिकार, डिजिटल वास्तुकार, संगठनात्मक रूप से सबसे चुस्त, ग्राहक केंद्रित, डेटा अधिवक्ता, डिजिटल कार्यस्थल लैंडस्केपर और व्यवसाय प्रक्रिया अनुकूलक।

डायोड ट्रांजिस्टर लॉजिक सर्किट

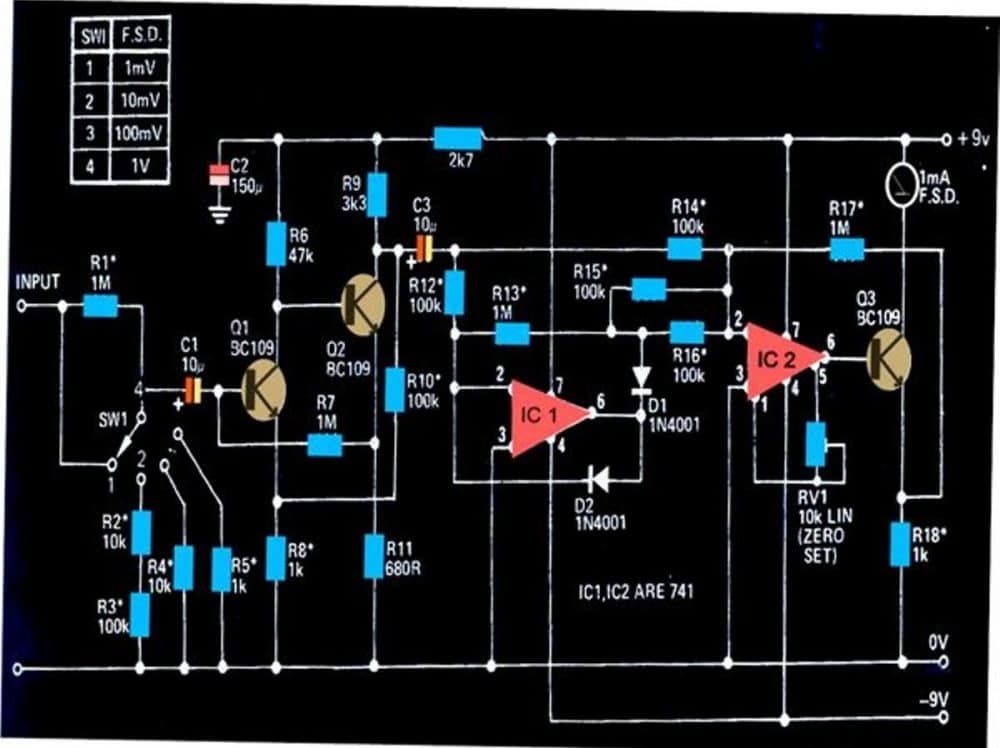

डायोड ट्रांजिस्टर लॉजिक सर्किट नीचे दिखाया गया है। यह एक दो-इनपुट डायोड ट्रांजिस्टर लॉजिक NAND गेट सर्किट है। यह सर्किट दो डायोड और एक ट्रांजिस्टर के साथ डिज़ाइन किया गया है जहां दो डायोड को D1, और D2 के साथ इंगित किया गया है और अवरोधक को R1 के साथ इंगित किया गया है जो लॉजिक सर्किट का इनपुट पक्ष बनाता है। Q1 ट्रांजिस्टर CE कॉन्फ़िगरेशन और R2 अवरोधक आउटपुट पक्ष बनाते हैं। इस सर्किट में 'C1' कैपेसिटर का उपयोग स्विचिंग समय के दौरान ओवरड्राइव करंट देने के लिए किया जाता है और इससे स्विचिंग समय कुछ स्तर तक कम हो जाता है।

डायोड ट्रांजिस्टर लॉजिक वर्किंग

जब भी सर्किट A और B के दोनों इनपुट LOW हैं, तो D1 और D2 दोनों डायोड फॉरवर्ड बायस्ड हो जाएंगे, इस प्रकार ये डायोड आगे की दिशा में संचालित होंगे। इस प्रकार वोल्टेज आपूर्ति (+VCC = 5V) के कारण वर्तमान आपूर्ति R1 रोकनेवाला और दो डायोड में GND को आपूर्ति करेगी। R1 अवरोधक के भीतर वोल्टेज की आपूर्ति कम हो जाती है और यह Q1 ट्रांजिस्टर को चालू करने के लिए पर्याप्त नहीं होगी, इस प्रकार Q1 ट्रांजिस्टर कट-ऑफ मोड में होगा। तो, 'Y' टर्मिनल पर ओ/पी लॉजिक 1 या उच्च मान होगा।

जब कोई भी एक इनपुट LOW होता है, तो संबंधित डायोड फॉरवर्ड-बायस्ड होगा, इसलिए एक समान ऑपरेशन होगा। चूंकि इनमें से कोई भी डायोड फॉरवर्ड बायस्ड है, तो करंट को फॉरवर्ड-बायस्ड डायोड में जमीन पर आपूर्ति की जाएगी, इस प्रकार 'Q1' ट्रांजिस्टर कट-ऑफ मोड के भीतर होगा, इसलिए 'Y' टर्मिनल पर आउटपुट होगा उच्च या तर्क 1.

जब भी ए और बी दोनों इनपुट उच्च होंगे तो दोनों डायोड रिवर्स बायस्ड हो जाएंगे, इस प्रकार दोनों डायोड संचालन नहीं करेंगे। तो इस स्थिति में, +VCC आपूर्ति से वोल्टेज Q1 ट्रांजिस्टर को चालन मोड में चलाने के लिए पर्याप्त होगा।

इसलिए ट्रांजिस्टर पूरे उत्सर्जक और संग्राहक टर्मिनलों पर संचालन करता है। पूरा वोल्टेज 'R2' रेसिस्टर के भीतर कम हो जाता है और 'Y' टर्मिनल पर आउटपुट में LOW o/p होगा और इसे कम या लॉजिक 0 माना जाता है।

ट्रुथ टेबल

डीटीएल सत्य तालिका नीचे दिखाई गई है।

|

ए |

बी | और |

|

0 |

0 | 1 |

|

0 |

1 |

1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

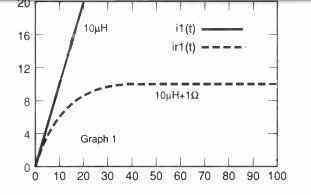

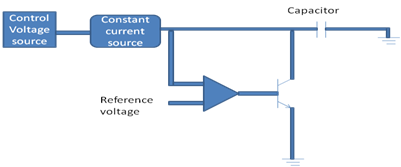

डायोड ट्रांजिस्टर तर्क प्रसार विलंब काफी बड़ा है। जब भी सभी इनपुट लॉजिक हाई होते हैं तो ट्रांजिस्टर संतृप्ति में चला जाएगा और आधार क्षेत्र के भीतर चार्ज बिल्ड-अप हो जाएगा। जब भी एक इनपुट कम हो तो प्रसार समय को बदलते हुए इस चार्ज को हटा देना चाहिए। डायोड ट्रांजिस्टर लॉजिक को एक तरह से गति देने की तकनीक में प्रतिरोधक R3 पर एक संधारित्र जोड़ना शामिल है। यहां, यह संधारित्र बेस टर्मिनल पर संचित चार्ज को समाप्त करके ट्रांजिस्टर को बंद करने में सहायता करता है। इस सर्किट में कैपेसिटर पहले बेस ड्राइव को बढ़ाकर ट्रांजिस्टर को चालू करने में भी सहायता करता है।

संशोधित डायोड ट्रांजिस्टर तर्क

संशोधित DTL NAND गेट नीचे दिखाया गया है। प्रतिरोधक और कैपेसिटर घटकों के बड़े मूल्यों को आईसी पर आर्थिक रूप से तैयार करना बहुत मुश्किल है। तो निम्नलिखित DTL NAND गेट सर्किट को C1 कैपेसिटर को हटाकर, अवरोधक के मान को कम करके और IC के कार्यान्वयन के लिए संशोधित किया जा सकता है ट्रांजिस्टर और डायोड जहां भी संभव हो। यह संशोधित सर्किट केवल एक सकारात्मक आपूर्ति का उपयोग करता है और इस सर्किट में D1, और D2 डायोड, एक R3 रोकनेवाला और एक AND गेट के साथ एक इनपुट चरण शामिल होता है जिसे एक ट्रांजिस्टरयुक्त इन्वर्टर के माध्यम से पालन किया जाता है।

कार्यरत

इस सर्किट की कार्यप्रणाली इस प्रकार है, इस सर्किट में दो इनपुट टर्मिनल A और B हैं, और A और B जैसे इनपुट वोल्टेज या तो उच्च या निम्न हो सकते हैं।

यदि दोनों इनपुट ए और बी कम या तर्क 0 हैं, तो दोनों डायोड आगे की ओर पक्षपाती हो जाएंगे, इस प्रकार 'एम' पर क्षमता एक डायोड की वोल्टेज ड्रॉप है जो 0.7 वी है। हालांकि चालन में 'क्यू' ट्रांजिस्टर को चलाने के लिए , तो हमें डायोड डी3, डी4 और 'क्यू' ट्रांजिस्टर के बीई जंक्शन को आगे बायस करने के लिए 2.1 वी की आवश्यकता है, इस प्रकार यह ट्रांजिस्टर कटऑफ है और आउटपुट वाई = 1 प्रदान करता है

Y = Vcc = तर्क 1 और A = B = 0 के लिए, Y = 1 या उच्च।

यदि A या B में से कोई भी इनपुट कम है, तो किसी भी इनपुट को +Vcc से जुड़े किसी भी टर्मिनल के साथ GND से जोड़ा जा सकता है, समतुल्य डायोड संचालित होगा, और VM ≅ 0.7 V और Q ट्रांजिस्टर कट जाएगा , और आउटपुट 'Y' = 1 या लॉजिक हाई प्रदान करें।

यदि A = 0 और B =1 (या) यदि A = 1 और B = 0 है, तो आउटपुट Y = 1 या उच्च है।

यदि A और B दोनों जैसे दो इनपुट उच्च हैं और A और B दोनों केवल + Vcc से जुड़े हैं, तो D1 और D2 दोनों डायोड रिवर्स-आधारित होंगे और वे संचालन नहीं करते हैं। डी3 और डी4 डायोड फॉरवर्ड बायस्ड हैं और बेस टर्मिनल पर करंट केवल आरडी, डी3 और डी4 के माध्यम से क्यू ट्रांजिस्टर को आपूर्ति की जाती है। ट्रांजिस्टर को संतृप्ति में चलाया जा सकता है और ओ/पी वोल्टेज कम वोल्टेज होगा।

ए = बी = 1 के लिए, आउटपुट वाई = 0 या कम।

संशोधित डीटीएल के अनुप्रयोगों में निम्नलिखित शामिल हैं।

लॉजिक हाई कंडीशन के साथ उच्च प्रतिबाधा वाले बाद के गेटों के कारण अधिक फैन आउट संभव है। इस सर्किट में बेहतर शोर प्रतिरोधक क्षमता है। रेसिस्टर्स और कैपेसिटर के बजाय कई डायोड का उपयोग इस सर्किट को एकीकृत सर्किट फॉर्म के भीतर बहुत किफायती बना देगा।

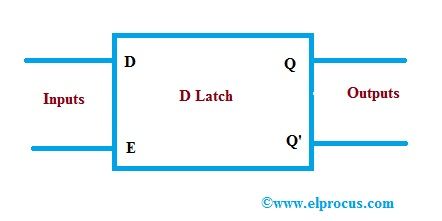

डायोड ट्रांजिस्टर लॉजिक NOR गेट

डायोड ट्रांजिस्टर लॉजिक NOR गेट को ट्रांजिस्टर इन्वर्टर के साथ DRL या गेट के साथ DTL NAND गेट के समान डिज़ाइन किया गया है। एक सामान्य आउटपुट के माध्यम से विभिन्न डीटीएल इनवर्टर को मिलाकर डीटीएल एनओआर सर्किट को और अधिक सुंदर ढंग से डिजाइन किया जा सकता है। इस तरीके से, NOR गेट के लिए आवश्यक इनपुट देने के लिए कई इनवर्टर को एकजुट किया जा सकता है।

इस सर्किट को डीटीएल इन्वर्टर सर्किट के अलावा अन्य घटकों के साथ डिजाइन किया जा सकता है बिजली की आपूर्ति और दो 4.7 K प्रतिरोधों , 1एन914 या 1एन4148 सिलिकॉन डायोड. नीचे दिखाए गए सर्किट के अनुसार सर्किट कनेक्ट करें।

कार्यरत

एक बार कनेक्शन बन जाने के बाद, सर्किट को बिजली की आपूर्ति प्रदान करने की आवश्यकता होती है। उसके बाद, डिप स्विच के साथ बिजली आपूर्ति से ए और बी पर चार संभावित इनपुट संयोजन लागू करें। अब प्रत्येक इनपुट संयोजन के लिए, आउटपुट 'क्यू' की तार्किक स्थिति को नोट करने की आवश्यकता है जैसा कि दर्शाया गया है नेतृत्व किया और उस आउटपुट को रिकॉर्ड करें। परिणामों की तुलना NOR गेट ऑपरेशन से करें। एक बार जब आप अपना अवलोकन पूरा कर लें, तो बिजली की आपूर्ति बंद कर दें।

|

ए |

बी |

वाई = (ए+बी)' |

|

0 |

0 | 1 |

|

0 |

1 | 0 |

| 1 | 0 |

0 |

| 1 | 1 |

0 |

डायोड ट्रांजिस्टर तर्क और गेट

डायोड ट्रांजिस्टर लॉजिक और गेट नीचे दिखाया गया है। इस सर्किट में, तर्क इस प्रकार है; 1 और 0 को +5V सकारात्मक तर्क और 0V के अनुरूप लिया जाता है।

जब भी A1, A2 (या) A3 से कोई इनपुट लो लॉजिक स्थिति में होता है तो उस इनपुट से जुड़ा डायोड फॉरवर्ड बायस में होगा, उसके बाद ट्रांजिस्टर कट ऑफ में आ जाएगा और आउटपुट लो या लॉजिक 0 होगा। इसी तरह, यदि सभी तीन इनपुट तर्क 1 पर हैं तो कोई भी डायोड आचरण नहीं करता है और ट्रांजिस्टर भारी संचालन करता है। उसके बाद, ट्रांजिस्टर संतृप्त हो जाता है और आउटपुट उच्च या तर्क 1 होगा।

डायोड ट्रांजिस्टर लॉजिक और गेट की सत्य तालिका नीचे दिखाई गई है।

|

ए 1 |

ए2 | ए3 |

वाई = ए.बी |

|

0 |

0 | 0 | 0 |

|

0 |

0 | 1 | 0 |

|

0 |

1 | 0 |

0 |

| 0 | 1 | 1 |

0 |

|

1 |

0 | 0 | 0 |

|

1 |

0 | 1 |

0 |

| 1 | 1 | 0 |

0 |

| 1 | 1 | 1 |

1 |

डीटीएल, टीटीएल और आरटीएल के बीच तुलना

डीटीएल, टीटीएल और आरटीएल के बीच अंतर पर नीचे चर्चा की गई है।

| डीटीएल | टीटीएल |

आरटीएल |

| DTL शब्द का अर्थ डायोड-ट्रांजिस्टर लॉजिक है। | टीटीएल शब्द का अर्थ ट्रांजिस्टर-ट्रांजिस्टर लॉजिक है। | RTL शब्द का अर्थ रेसिस्टर-ट्रांजिस्टर लॉजिक है। |

| डीटीएल में, लॉजिक गेट्स को पीएन जंक्शन डायोड और ट्रांजिस्टर के साथ डिज़ाइन किया गया है। | टीटीएल में, लॉजिक गेट्स को BJTs के साथ डिज़ाइन किया गया है।

|

आरटीएल में, लॉजिक गेट्स को रेसिस्टर और ट्रांजिस्टर के साथ डिज़ाइन किया गया है। |

| डीटीएल में, डायोड का उपयोग आई/पी घटकों के रूप में किया जाता है और ट्रांजिस्टर का उपयोग ओ/पी घटकों के रूप में किया जाता है। | टीटीएल में, एक ट्रांजिस्टर का उपयोग प्रवर्धन के लिए किया जाता है जबकि दूसरे ट्रांजिस्टर का उपयोग स्विचिंग उद्देश्यों के लिए किया जाता है। | आरटीएल में अवरोधक का उपयोग आई/पी घटक के रूप में किया जाता है और ट्रांजिस्टर का उपयोग ओ/पी घटक के रूप में किया जाता है |

| आरटीएल की तुलना में डीटीएल प्रतिक्रिया बेहतर है। | टीटीएल प्रतिक्रिया डीटीएल और आरटीएल से काफी बेहतर है। | आरटीएल प्रतिक्रिया धीमी है. |

| बिजली की हानि कम है. | इसमें बहुत कम बिजली हानि होती है। | बिजली की हानि अधिक है. |

| इसका निर्माण जटिल है. | इसका निर्माण बहुत ही सरल है. | इसका निर्माण सरल है. |

| डीटीएल न्यूनतम फैनआउट 8 है। | टीटीएल न्यूनतम फैनआउट 10 है। | आरटीएल न्यूनतम फैनआउट 5 है। |

| प्रत्येक गेट के लिए बिजली अपव्यय आम तौर पर 8 से 12 मेगावाट है। | प्रत्येक गेट के लिए बिजली अपव्यय आम तौर पर 12 से 22 मेगावाट है। | प्रत्येक गेट के लिए बिजली अपव्यय आम तौर पर 12 मेगावाट है। |

| इसकी ध्वनि प्रतिरोधक क्षमता अच्छी है। | इसकी ध्वनि प्रतिरोधक क्षमता बहुत अच्छी है। | इसकी ध्वनि प्रतिरोधक क्षमता मध्यम है। |

| गेट के लिए इसका सामान्य प्रसार विलंब 30 एनएस है। | गेट के लिए इसका सामान्य प्रसार विलंब 12 से 6 एनएस है। | गेट के लिए इसका सामान्य प्रसार विलंब 12 एनएस है। |

| इसका क्लॉक रेट 12 से 30 मेगाहर्ट्ज है। | इसका क्लॉक रेट 15 से 60 मेगाहर्ट्ज है। | इसका क्लॉक रेट 8 मेगाहर्ट्ज है। |

| इसमें कार्यों की संख्या काफी अधिक है। | इसमें कार्यों की संख्या बहुत अधिक है। | इसमें कार्यों की संख्या बहुत अधिक है। |

| डीटीएल लॉजिक का उपयोग बुनियादी स्विचिंग और डिजिटल सर्किट में किया जाता है। | टीटीएल लॉजिक का उपयोग आधुनिक डिजिटल सर्किट और एकीकृत सर्किट में किया जाता है। | RTL का उपयोग पुराने कंप्यूटरों में किया जाता है। |

लाभ

डायोड ट्रांजिस्टर लॉजिक सर्किट के फायदों में निम्नलिखित शामिल हैं।

- DTL की स्विचिंग गति RTL की तुलना में तेज़ है।

- डीटीएल सर्किट के भीतर डायोड का उपयोग उन्हें सस्ता बनाता है क्योंकि आईसी पर डायोड का निर्माण प्रतिरोधों और कैपेसिटर की तुलना में सरल है।

- डीटीएल सर्किट के भीतर बिजली की हानि बहुत कम है।

- डीटीएल सर्किट में तेज़ स्विचिंग गति होती है।

- डीटीएल में अधिक फैन-आउट और बेहतर शोर मार्जिन है।

डायोड ट्रांजिस्टर लॉजिक सर्किट के नुकसान निम्नलिखित को शामिल कीजिए।

- टीटीएल की तुलना में डीटीएल की परिचालन गति कम है।

- इसमें बहुत बड़ा गेट प्रसार विलंब है।

- उच्च इनपुट के लिए, DTL का आउटपुट संतृप्ति में चला जाता है।

- यह पूरे ऑपरेशन के दौरान गर्मी उत्पन्न करता है।

अनुप्रयोग

डायोड ट्रांजिस्टर तर्क के अनुप्रयोग निम्नलिखित को शामिल कीजिए।

- डायोड- ट्रांजिस्टर लॉजिक का उपयोग डिजिटल सर्किट को डिजाइन और निर्माण करने के लिए किया जाता है तर्क द्वार इनपुट चरण में डायोड और आउटपुट चरण में BJT का उपयोग करें।

- डीटीएल एक विशिष्ट प्रकार का सर्किट है जिसका उपयोग विद्युत संकेतों को संसाधित करने के लिए वर्तमान डिजिटल इलेक्ट्रॉनिक्स में किया जाता है।

- DTL का उपयोग सरल लॉजिक सर्किट बनाने के लिए किया जाता है।

इस प्रकार, यह है डायोड ट्रांजिस्टर तर्क का अवलोकन , सर्किट, कार्य, फायदे, नुकसान और अनुप्रयोग। आरटीएल सर्किट की तुलना में डीटीएल सर्किट अधिक जटिल होते हैं, लेकिन इसकी बेहतर फैन आउट क्षमता और बढ़े हुए शोर मार्जिन के कारण इस तर्क ने आरटीएल को बदल दिया है, लेकिन डीटीएल की गति धीमी है। यहां आपके लिए एक प्रश्न है कि आरटीएल क्या है?