आम तौर पर, पूर्ण घटाव सबसे अधिक इस्तेमाल किया और आवश्यक संयोजन तर्क सर्किट । यह एक बुनियादी इलेक्ट्रॉनिक उपकरण है, जिसका उपयोग दो बाइनरी संख्याओं के घटाव को करने के लिए किया जाता है। पहले के लेख में, पहले से ही हमने मूल सिद्धांत दिया है आधा योजक और एक पूर्ण योजक जो गणना के लिए द्विआधारी अंकों का उपयोग करता है। इसी तरह, पूर्ण-घटाव द्विआधारी अंकों का उपयोग करता है जैसे घटाव के लिए 0,1। इसका सर्किट OR, Ex-OR, NAND गेट जैसे लॉजिक गेट के साथ बनाया जा सकता है। इस सबट्रेक्टर के इनपुट ए, बी, बिन और आउटपुट डी, बाउट हैं।

यह लेख एक पूर्ण-सबट्रैक्टर सिद्धांत विचार देता है जिसमें परिसर शामिल होता है जैसे कि एक सबट्रैक्टर, लॉजिक गेट के साथ डिज़ाइन, सत्य तालिका आदि। यह आलेख इंजीनियरिंग छात्रों के लिए उपयोगी है जो एचडीएल प्रैक्टिकल लैब में इन विषयों से गुजर सकते हैं।

सबट्रैक्टर क्या है?

बाइनरी अंक घटाव को घटाव सर्किट की मदद से किया जा सकता है। यह एक प्रकार का कॉम्बिनेशन लॉजिक सर्किट है, जिसका उपयोग दो बाइनरी अंकों जैसे 0 और 1 एस के घटाव को करने के लिए किया जाता है। 0 से 0 या 0 से बाइनरी अंकों का घटाव परिणाम में परिवर्तन नहीं करता है, 1 से 1 के घटाव का परिणाम 0 के रूप में होगा, लेकिन 1 से 0 के घटाव को उधार की आवश्यकता होती है।

उदाहरण के लिए, दो-बिट सबट्रैक्टर सर्किट में ए और बी जैसे दो इनपुट शामिल हैं जबकि आउटपुट अंतर और उधार हैं। इस सर्किट को इनवर्टर के साथ योजक के साथ बनाया जा सकता है जो प्रत्येक डेटा इनपुट के साथ-साथ एफए के पहले चरण के उधार (बिन) इनपुट के बीच स्थित हैं।

सबट्रैक्टर को दो प्रकारों में वर्गीकृत किया जाता है जैसे आधा सबट्रैक्टर और फुल सबट्रैक्टर। यहां हम पूर्ण घटाव पर चर्चा कर रहे हैं।

एक पूर्ण उपशीर्षक क्या है?

यह एक इलेक्ट्रॉनिक उपकरण है या तर्क सर्किट जो दो बाइनरी अंकों का घटाव करता है। यह डिजिटल इलेक्ट्रॉनिक्स में इस्तेमाल किया जाने वाला एक कॉम्बिनेशन लॉजिक सर्किट है। कई कॉम्बिनेशन सर्किट में उपलब्ध हैं एकीकृत सर्किट प्रौद्योगिकी योजक, एनकोडर, डिकोडर और मल्टीप्लेक्सर्स। इस लेख में, हम आधे घटाव का उपयोग करके इसके निर्माण पर चर्चा करने जा रहे हैं और साथ ही सत्य तालिका जैसी शर्तें भी।

पूर्ण घटाव

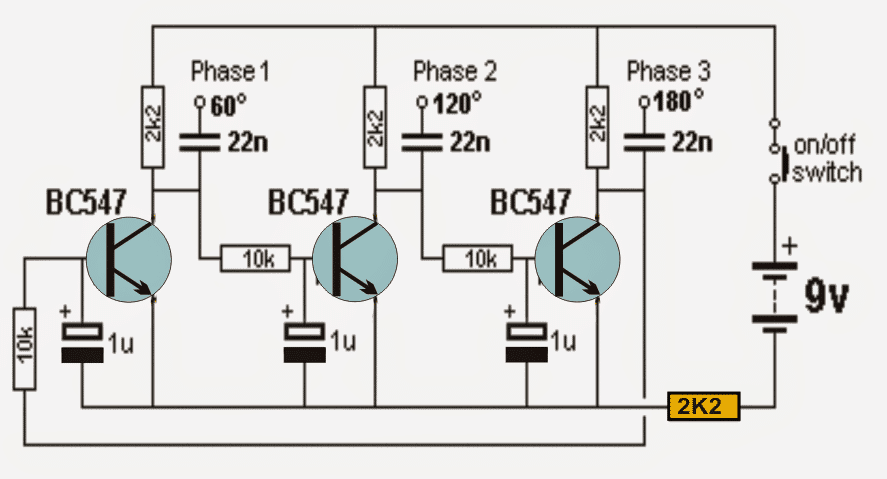

इस का डिज़ाइन दो आधा घटाव द्वारा किया जा सकता है, जिसमें तीन इनपुट जैसे कि minuend, subtrahend, और उधार लेना, इनपुट के बीच उधार बिट बिट दो बाइनरी अंकों के घटाव से प्राप्त होता है और अगले उच्च-क्रम जोड़ी से घटाया जाता है। बिट्स, अंतर के रूप में आउटपुट और उधार।

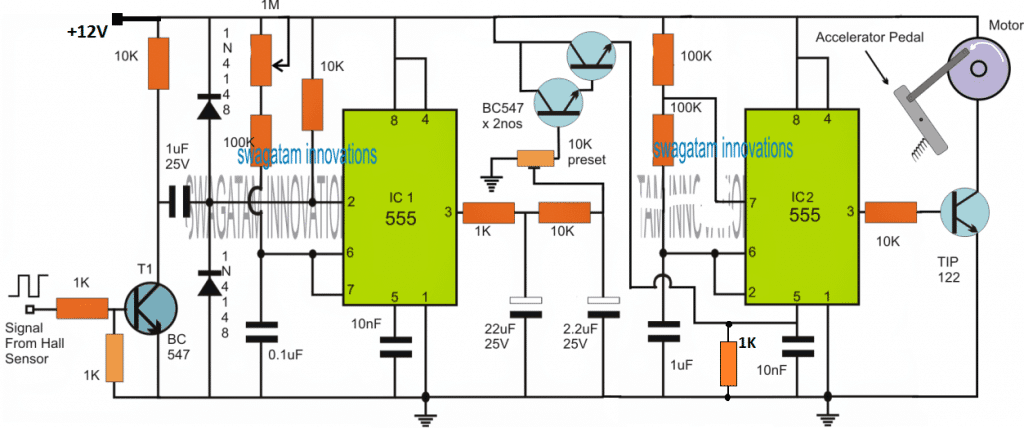

पूर्ण सबट्रैक्टर ब्लॉक आरेख नीचे दिखाया गया है। आधे सबट्रैक्टर का सबसे बड़ा नुकसान यह है कि हम इस सबट्रैक्टर में बॉरो बिट नहीं बना सकते हैं। जबकि इसके डिजाइन में, वास्तव में हम सर्किट में बॉरो बिट बना सकते हैं और शेष दो i / ps के साथ घटा सकते हैं। यहाँ A, minuend है, B सबट्रेंडेंड है और बिन में उधार लिया गया है। आउटपुट अंतर (डिफ) और Bout (बॉरो आउट) हैं। एक अतिरिक्त या गेट के साथ दो आधा घटाव का उपयोग करके पूर्ण सबट्रैक्टर सर्किट प्राप्त कर सकता है।

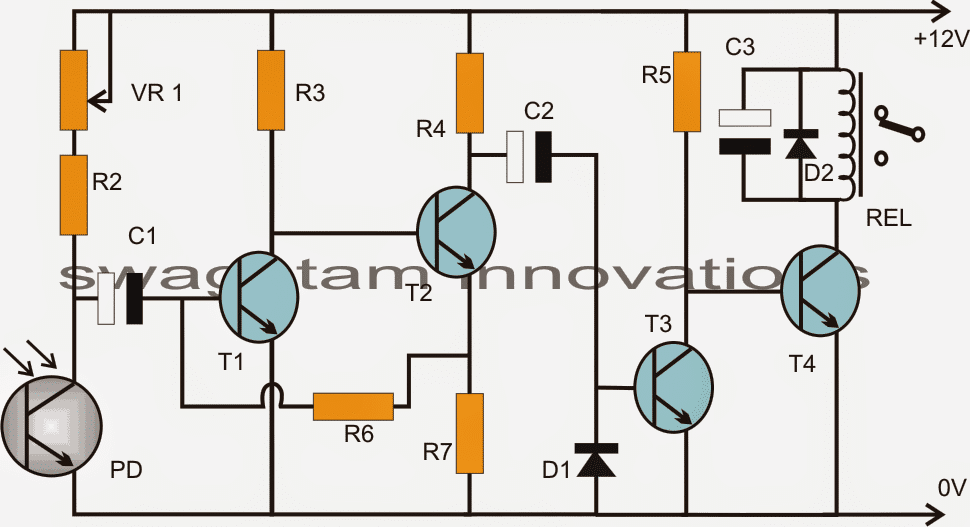

तर्क गेट्स के साथ पूर्ण सबट्रैक्टर सर्किट आरेख

बेसिक गेट का उपयोग करके पूर्ण घटाव का सर्किट आरेख s को निम्नलिखित ब्लॉक आरेख में दिखाया गया है। यह सर्किट दो आधा-घटाव सर्किट के साथ किया जा सकता है।

प्रारंभिक आधे-घटाव सर्किट में, द्विआधारी इनपुट ए और बी हैं जैसा कि हमने पिछले आधे-घटाव लेख में चर्चा की है, यह दो आउटपुट उत्पन्न करेगा, अर्थात् अंतर (डिफ) और बॉरो।

तर्क गेट्स का उपयोग करके पूर्ण सबट्रैक्टर

बाएं सबट्रैक्टर का अंतर o / p लेफ्ट हाफ-सबट्रैक्टर सर्किट को दिया जाता है। डिफ आउटपुट को आगे दाएं आधे सबट्रैक्टर सर्किट के इनपुट के लिए प्रदान किया गया है। हमने अगले I / p के दूसरे हिस्से में बिट का प्रस्ताव दिया आधा घटाव सर्किट । एक बार और यह डिफ को आउट करने के साथ-साथ बिट को थोड़ा बाहर कर देगा। इस सबट्रैक्टर का अंतिम आउटपुट डिफ-आउटपुट है।

दूसरी ओर, दोनों आधा सबट्रैक्टर सर्किटों में से बॉरो OR लॉजिक गेट से जुड़ा है। बाद में सबट्रैक्टर के दो आउटपुट बिट्स के लिए OR लॉजिक देने के बजाय, हम सबट्रेक्टर से अंतिम बॉरो को प्राप्त करते हैं। MSB (एक सबसे महत्वपूर्ण बिट) को सूचित करने के लिए अंतिम उधार।

यदि हम इसके आंतरिक परिपथ का निरीक्षण करते हैं, तो हम एक अतिरिक्त OR गेट के साथ NAND गेट और XOR गेट के साथ दो हाफ सबट्रेक्टर्स देख सकते हैं।

पूर्ण सबट्रैक्टर सत्य तालिका

इस घटाव सर्किट दो बिट्स के बीच एक घटाव निष्पादित करता है, जिसमें 3- इनपुट (ए, बी, और बिन) और दो आउटपुट (डी और बाउट) होते हैं। यहां इनपुट्स मिनुएड, सबट्रेंड और पिछले उधार को इंगित करते हैं, जबकि दो आउटपुट को उधार ओ / पी और अंतर के रूप में दर्शाया जाता है। निम्न छवि पूर्ण-घटाव की सत्य तालिका दिखाती है।

इनपुट | आउटपुट | |||

Minuend (A) | सबट्रेंडेंड (B) | उधार (बिन) | अंतर (D) | उधार (बाउट) |

० | ० | ० | ० | ० |

० | ० | 1 | 1 | 1 |

| ० | 1 | ० | 1 | 1 |

| ० | 1 | 1 | ० | 1 |

1 | ० | ० | 1 | ० |

| 1 | ० | 1 | ० | ० |

1 | 1 | ० | ० | ० |

1 | 1 | 1 | 1 | 1 |

कश्मीर का नक्शा

का सरलीकरण पूर्ण घटाव K- नक्शा उपरोक्त अंतर और उधार के लिए नीचे दिखाया गया है।

अंतर के साथ-साथ बिन के समीकरणों का उल्लेख नीचे किया गया है।

अंतर के लिए अभिव्यक्ति है,

D = A'B’Bin + AB'Bin '+ A'BBin' + ABBin

उधार के लिए अभिव्यक्ति है,

Bout = A'Bin + A'B + BBin

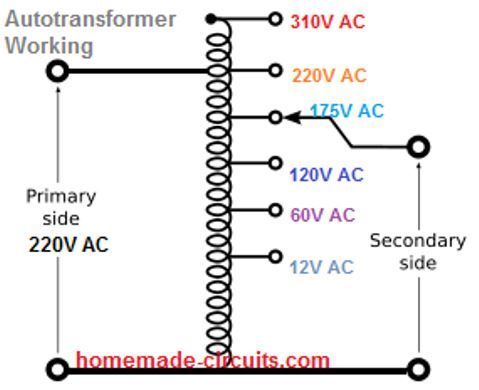

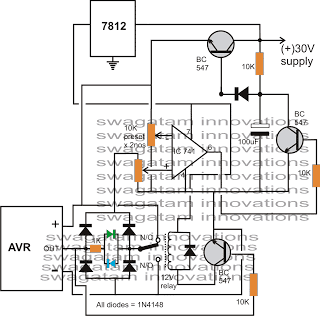

फुल सबट्रैक्टर सर्किट का कैस्केडिंग

इससे पहले, हमने लॉजिक गेट्स के साथ कंस्ट्रक्शन, सर्किट डायग्राम जैसे अवलोकन पर चर्चा की है। लेकिन अगर हम दो अन्यथा कम से कम 1-बिट संख्या घटाना चाहते हैं, तो यह सबट्रैक्टर सर्किट सिंगल बिट संख्याओं को कैस्केड करने में बहुत सहायक है और दो से अधिक बाइनरी संख्याओं को घटाता है। ऐसे मामलों में, एक पूर्ण योजक कैस्केड सर्किट का उपयोग NOT लॉजिक गेट की मदद से किया जाता है। पूर्ण योजक से पूर्ण घटाव तक सर्किट का रूपांतरण 2 की पूरक तकनीक का उपयोग करके किया जा सकता है।

आम तौर पर, पूर्ण योजक के लिए सबट्रेन्ड इनपुट को उलटा करें, न कि गेट का उपयोग करके अन्यथा एक इन्वर्टर। इस Minuend (noninverted इनपुट) और Subtrahend (इनवर्टेड इनपुट) को जोड़कर, FA सर्किट का LSB (कैरी इनपुट) 1 है, जिसका अर्थ है कि तर्क उच्च है अन्यथा हम 2 की पूरक तकनीक का उपयोग करके दो बाइनरी अंकों को घटाते हैं। एफए का आउटपुट डिफ बिट है और अगर हम कैरी आउट कर देते हैं तो हम एमएसबी अन्यथा बॉरो बिट प्राप्त कर सकते हैं। दरअसल, हम सर्किट को डिजाइन कर सकते हैं ताकि आउटपुट का अवलोकन किया जा सके।

वेरिलोग कोड

कोडिंग भाग के लिए, पहले, हमें तर्क सर्किट आरेख के मॉडलिंग के संरचनात्मक तरीके की जांच करने की आवश्यकता है। इसके लॉजिक आरेख को AND गेट, हाफ सबट्रैक्टर सर्किट और AND, OR, NOT, XOR गेट्स जैसे लॉजिक गेट्स का उपयोग करके बनाया जा सकता है। जैसा कि संरचनात्मक मॉडलिंग में, हम हर बुनियादी मौलिक व्यवस्था के लिए विभिन्न मॉड्यूल की व्याख्या करते हैं। निम्नलिखित कोड में, प्रत्येक गेट के लिए अलग-अलग मॉड्यूल परिभाषित किए जा सकते हैं।

यह मॉड्यूल OR गेट के लिए है।

INPUT: a0, b0

OUTPUT: c0

अंत में, हम इन गेट सटीक मॉड्यूल को एक ही मॉड्यूल में एकजुट करेंगे। उसके लिए, यहाँ हम मॉड्यूल की तात्कालिकता का उपयोग करते हैं। एक बार हम सटीक इनपुट या विविध इनपुट सेट के लिए कार्य करना चाहते हैं, तो इस तात्कालिकता का उपयोग किया जा सकता है। सबसे पहले, हम एक आधा सबट्रैक्टर डिजाइन करते हैं फिर इस मॉड्यूल का उपयोग एक पूर्ण सबट्रैक्टर को लागू करने के लिए किया जाता है। इसे लागू करने के लिए, हम Bout के चर के लिए o / ps को संयोजित करने के लिए OR गेट का उपयोग करते हैं। पूर्ण सबट्रैक्टर के लिए वेरिलॉग कोड नीचे दिखाया गया है

मॉड्यूल or_gate (a0, b0, c0)

इनपुट a0, b0

आउटपुट c0

असाइन c0 = a0 | b0

अंतर्मुखी

मॉड्यूल xor_gate (a1, b1, c1)

इनपुट a1, b1

आउटपुट c1

c1 = a1 ^ b1 असाइन करें

अंतर्मुखी

मॉड्यूल और_गेट (a2, b2, c2)

इनपुट a2, b2

आउटपुट c2

c2 = a2 & b2 असाइन करें

अंतर्मुखी

मॉड्यूल not_gate (a3, b3)

इनपुट a3

आउटपुट b3

b3 = ~ a3 असाइन करें

अंतर्मुखी

मॉड्यूल half_subtractor (a4, b4, c4, d4)

इनपुट a4, b4

आउटपुट c4, d4

तार x

xor_gate u1 (a4, b4, c4)

और_गेट u2 (x, b4, d4)

not_gate u3 (a4, x)

अंतर्मुखी

मॉड्यूल full_subtractor (A, B, Bin, D, Bout)

इनपुट A, B, बिन

आउटपुट डी, बाउट

वायर पी, क्यू, आर

आधा_उपयोगकर्ता u4 (ए, बी, पी, क्यू)

आधा_उपयोगकर्ता u5 (पी, बिन, डी, आर)

or_gate u6 (q, r, Bout)

अंतर्मुखी

4X1 मल्टीप्लेक्सर का उपयोग करके पूर्ण सबट्रैक्टर

घटाव का निष्पादन दो के पूरक विधि के माध्यम से किया जा सकता है। इस प्रकार हमें 1-XOR गेट का उपयोग करने की आवश्यकता होती है जो 1-बिट को पलटने के लिए उपयोग किया जाता है और एक को कैरी बिट में शामिल करता है। DIFFERENCE का आउटपुट पूर्ण योजक सर्किट में आउटपुट SUM के समान है, हालांकि BARROW o / p पूर्ण योजक के कैरी आउटपुट के समान नहीं है, हालांकि यह उलटा है और साथ ही इसकी तारीफ भी करता है, जैसे A - B + A + (-B) = A + दो B का पूरक है।

4X1 मल्टीप्लेक्सर का उपयोग करते हुए इसका डिज़ाइन निम्नलिखित तर्क आरेख में दिखाया गया है। यह डिज़ाइन निम्नलिखित चरणों का उपयोग करके किया जा सकता है।

4X1 मल्टीप्लेक्स

- चरण 1 में, उप और बॉरो जैसे दो आउटपुट हैं। इसलिए हमें 2 मल्टीप्लेक्सर्स चुनना होगा।

- Step2 में, सत्य-तालिका को K-Maps के साथ लागू किया जा सकता है

- चरण 3 में, दो चर को आपकी चयनित रेखा के रूप में चुना जा सकता है। उदाहरण के लिए, B & C इस मामले में हैं।

सच्ची तालिका

पूर्ण घटाव की सत्य तालिका 4X1 मल्टीप्लेक्स का उपयोग करने वाले सर्किट में निम्नलिखित शामिल हैं

सेवा मेरे | ख | सी | विषय | उधार |

० | ० | ० | ० | ० |

| ० | ० | 1 | 1 | 1 |

| ० | 1 | ० | 1 | 1 |

० | 1 | 1 | ० | 1 |

| 1 | ० | ० | 1 | ० |

1 | ० | 1 | ० | ० |

| 1 | 1 | ० | ० | ० |

1 | 1 | 1 | 1 | 1 |

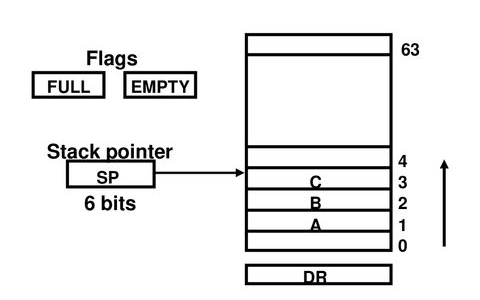

डिकोडर का उपयोग करके पूर्ण सबट्रैक्टर

3-8 डिकोडर्स का उपयोग करके एक पूर्ण सबट्रैक्टर का डिज़ाइन सक्रिय कम आउटपुट का उपयोग करके किया जा सकता है। निम्नलिखित तर्क आरेख का उपयोग करके डिकोडर के कामकाज को मान लें। डिकोडर में 3-8 डिकोडर में तीन इनपुट शामिल हैं। सत्य तालिका के आधार पर, हम अंतर और उधार के आउटपुट के लिए मिन्टरम लिख सकते हैं।

उपरोक्त सत्य तालिका से,

सत्य तालिका में अलग-अलग कार्यों के लिए, खदानों को 1,2,4,7 के रूप में लिखा जा सकता है, और इसी तरह, उधार के लिए, खदानों को 1,2,3,7 के रूप में लिखा जा सकता है। 3-8 डिकोडर्स में तीन इनपुट और साथ ही 8 आउटपुट लाइक 7 से 7 नंबर शामिल हैं।

3-से -8 विकोडक

यदि सबट्रैक्टर का इनपुट 000 है, तो आउटपुट will 0 'सक्रिय होगा और यदि इनपुट 001 है, तो आउटपुट then 1' सक्रिय होगा।

अब घटाव के आउटपुट को एक नंद द्वार से जोड़ने के लिए 1, 2, 4 और 7 से लिया जा सकता है, फिर आउटपुट में अंतर होगा। ये आउटपुट अन्य NAND लॉजिक गेट्स से कनेक्ट किए जा सकते हैं, जहाँ आउटपुट उधार में बदलता है।

उदाहरण के लिए, यदि इनपुट 001 है, तो आउटपुट 1 होगा अर्थात यह सक्रिय है। तो आउटपुट सक्रिय कम है और आउटपुट NAND गेट से प्राप्त किया जा सकता है जिसे उच्च और अंतर ऋण फ़ंक्शन जैसे अंतर फ़ंक्शन कहते हैं जो उच्च होने के लिए भी बदलते हैं। इसलिए हमें पसंदीदा आउटपुट मिलता है। तो अंत में, डिकोडर एक पूर्ण घटाव की तरह काम करता है।

फायदे और नुकसान

घटाव के फायदे निम्नलिखित को शामिल कीजिए।

- सबट्रैक्टर की डिजाइनिंग बहुत सरल होने के साथ-साथ कार्यान्वित भी होती है

- डीएसपी (डिजिटल सिग्नल प्रोसेसिंग) के भीतर बिजली कटौती

- कम्प्यूटेशनल कार्यों को उच्च गति से किया जा सकता है।

घटाव के नुकसान निम्नलिखित को शामिल कीजिए।

- आधे घटाव में, पहले चरण से बॉरो-जैसे इनपुट को स्वीकार करने की कोई शर्त नहीं है।

- सर्किट में देरी के माध्यम से घटाव की गति आंशिक हो सकती है।

अनुप्रयोग

कुछ के पूर्ण-घटाव के अनुप्रयोग निम्नलिखित को शामिल कीजिए

- ये आमतौर पर सर्किट में कठिनाई को कम करने के लिए ग्राफिक्स के अनुप्रयोगों के लिए CPU और GPU के रूप में घटाना करने के लिए कंप्यूटर में ALU (अंकगणितीय तर्क इकाई) के लिए नियोजित होते हैं।

- सबट्रेक्टर्स का उपयोग ज्यादातर इलेक्ट्रॉनिक उपकरणों और डिजिटल डिवाइसेस में घटाव जैसे अंकगणितीय कार्यों को करने के लिए किया जाता है।

- इसके लिए भी लागू हैं विभिन्न माइक्रोकंट्रोलर अंकगणितीय घटाव, समय और कार्यक्रम काउंटर (पीसी) के लिए

- तालिकाओं, पतों, आदि की गणना करने के लिए प्रोसेसर में सबट्रेक्टर का उपयोग किया जाता है।

- यह डीएसपी और नेटवर्किंग आधारित प्रणालियों के लिए भी उपयोगी है।

- इनका उपयोग मुख्य रूप से सर्किट की जटिलता को कम करने के लिए ग्राफिक्स अनुप्रयोगों के लिए सीपीयू और जीपीयू जैसे घटाव के लिए कंप्यूटर के भीतर ALU के लिए किया जाता है।

- इनका उपयोग मुख्य रूप से अंकगणितीय कार्यों को करने के लिए किया जाता है जैसे डिजिटल उपकरणों के भीतर घटाव, कैलकुलेटर इत्यादि।

- ये सबट्रेक्टर टाइमर, पीसी (प्रोग्राम काउंटर) और अंकगणितीय घटाव के लिए विभिन्न माइक्रोकंट्रोलर के लिए भी उपयुक्त हैं

- ये प्रोसेसर के लिए पते, टेबल आदि की गणना करने के लिए नियोजित होते हैं।

- NAND & NOR जैसे लॉजिक गेट के साथ इसे लागू करने का काम किसी भी पूर्ण सबट्रैक्टर लॉजिक सर्किट के साथ किया जा सकता है क्योंकि NOR और NAND गेट दोनों को यूनिवर्सल गेट कहा जाता है।

उपरोक्त जानकारी से, योजक का मूल्यांकन करके, दो आधा घटाव सर्किट का उपयोग करके पूर्ण घटाव, और इसके सारणीबद्ध रूप, कोई यह नोटिस कर सकता है कि पूर्ण-उप-योग में Dout पूर्ण-योजक के Sout के समान है। एकमात्र भिन्नता यह है कि पूर्ण-घटाव में A (इनपुट चर) पूरक है। इस प्रकार, पूर्ण-योजक सर्किट को पूर्ण-घटाव में बदलने के लिए इसे प्राप्त करने से पहले केवल i / p A को पूरक करने के लिए प्राप्त किया जा सकता है। तर्क फाटक अंतिम उधार-बिट आउटपुट (Bout) उत्पन्न करने के लिए।

किसी भी पूर्ण सबट्रैक्टर लॉजिक सर्किट का उपयोग करके, NAND गेट्स का उपयोग करके पूर्ण सबट्रैक्टर और न ही गेट्स का उपयोग करके पूर्ण सबट्रैक्टर को लागू किया जा सकता है, क्योंकि दोनों NAND और NOR गेट्स को सार्वभौमिक गेट्स के रूप में माना जाता है। यहां आपके लिए एक सवाल है, आधे सबट्रैक्टर और पूर्ण सबट्रैक्टर में क्या अंतर है?