इससे पहले, के डिजाइनिंग तर्क सर्किट का उपयोग करके किया जा सकता है एसएसआई (छोटे पैमाने पर एकीकरण) तर्क द्वार जैसे घटक, मल्टीप्लेक्सर , डी-मल्टीप्लेक्सर्स, एफएफ, आदि। लेकिन, अब एक पीएलडी इन सभी एसएसआई घटकों को बदल सकता है। तो यह PLD के साथ तुलना में SSI उद्योग को कम करने का कारण है, और इनका उपयोग कई अनुप्रयोगों में किया जाता है। प्रोग्रामेबल लॉजिक डिवाइस या पीएलडी लॉजिक सर्किट को लागू करने के लिए एक प्रकार की चिप का उपयोग किया जाता है। इसमें तर्क सर्किट तत्वों का एक सेट शामिल है जिसे कई तरीकों से संशोधित किया जा सकता है। एक PLD को ब्लैक बॉक्स की तरह देखा जाता है जिसमें प्रोग्रामेबल स्विच के साथ-साथ लॉजिक गेट भी होते हैं। स्विच का मुख्य कार्य PLD के भीतर लॉजिक गेट्स को लॉजिक सर्किट को निष्पादित करने के लिए पारस्परिक रूप से संबद्ध करने देना है। PLD को SPLD- सरल PLD जैसे विभिन्न प्रकारों में वर्गीकृत किया जाता है ( पीएलए और पाल ), CPLD- जटिल PLD , FPGAs- प्रोग्राम प्रोग्राम गेट एरेज़ । इस लेख में चर्चा की गई है कि एक PAL और PLA, डिज़ाइन और उनके अंतर क्या हैं।

पाल और पीएलए क्या हैं?

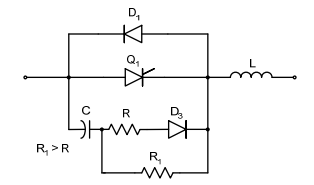

दोनों प्रोग्रामेबल एरे लॉजिक तथा प्रोग्राम करने योग्य तर्क PLDs (प्रोग्रामेबल लॉजिक डिवाइस) के प्रकार हैं, और इन्हें मुख्य रूप से क्रमिक लॉजिक द्वारा परस्पर संयोजन लॉजिक डिजाइन करने के लिए उपयोग किया जाता है। इन दोनों में मुख्य अंतर यह है कि PAL को AND गेटों के संग्रह और OR गेटों के निश्चित संग्रह के साथ डिज़ाइन किया जा सकता है, जबकि PLA को AND के एक प्रोग्राम योग्य सरणी के साथ डिज़ाइन किया जा सकता है और यद्यपि OR गेट का एक निश्चित संग्रह। एक प्रोग्रामेबल लॉजिक डिवाइस एक सरल और साथ ही लचीली लॉजिक सर्किट डिजाइनिंग प्रदान करता है।

प्रोग्रामेबल एरे लॉजिक

प्रोग्राम तर्क उपकरणों से पहले, द कॉम्बिनेशन लॉजिक सर्किट मल्टीप्लेक्सर्स के साथ डिज़ाइन किया जा सकता है, और ये सर्किट कठोर होने के साथ-साथ यौगिक भी हैं, फिर PLD विकसित किए जाते हैं। प्रारंभिक प्रोग्रामेबल लॉजिक डिवाइस ROM था, लेकिन यह हार्डवेयर अपव्यय मुद्दों के साथ-साथ हर हार्डवेयर अनुप्रयोग में घातीय वृद्धि वृद्धि के कारण सफल नहीं था। इस समस्या को दूर करने के लिए, PAL और PLA का उपयोग किया गया था। ये दो प्रोग्राम करने योग्य हैं, और कुशलता से हार्डवेयर का उपयोग करते हैं।

प्रोग्राम करने योग्य तर्क

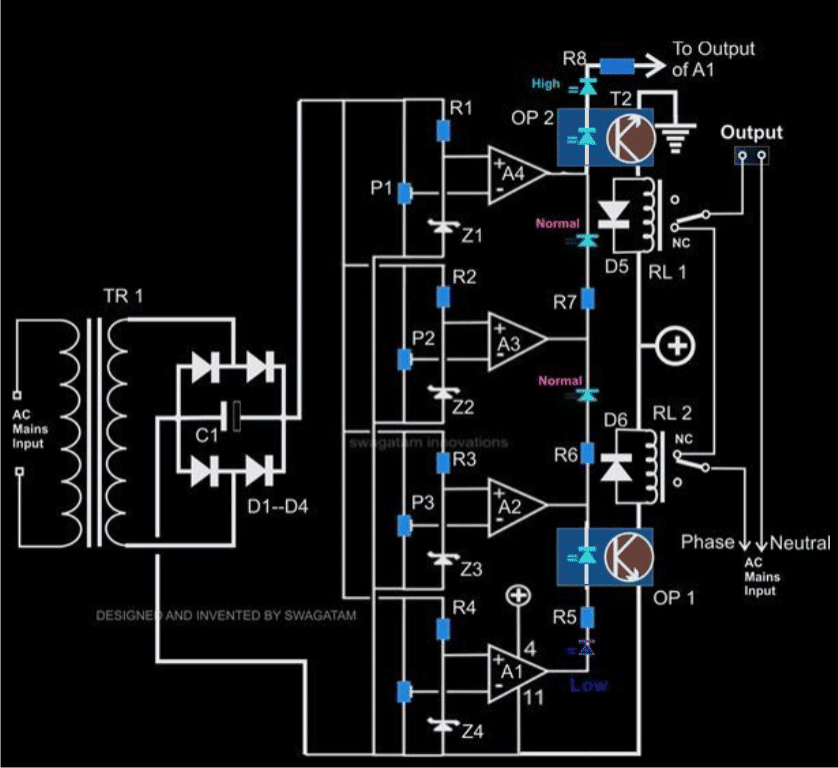

प्रोग्रामेबल एरे लॉजिक (पाल) का डिजाइन

पाल या प्रोग्रामेबल एरे लॉजिक शब्द की परिभाषा एक प्रकार का PLD है जिसे प्रोग्रामेबल लॉजिक डिवाइस सर्किट के रूप में जाना जाता है, और इस PAL का कार्य PLA के समान है। प्रोग्रामेबल एरे लॉजिक की डिजाइनिंग को फिक्स्ड या गेट्स के साथ-साथ प्रोग्रामेबल और गेट्स के साथ किया जा सकता है। इसका उपयोग करके हम दो आसान कार्यों को कार्यान्वित कर सकते हैं, जहां प्रत्येक OR गेट के साथ सहयोगी और द्वार उत्पाद की स्थितियों की उच्चतम संख्या को दर्शाते हैं जो कि निर्माण के रूप में उत्पन्न हो सकते हैं SOP (उत्पाद का योग) एक सटीक कार्य का।

जैसा कि तर्क गेट्स की तरह और लगातार गेट्स से जुड़ा हुआ है, और यह दर्शाता है कि उत्पादित उत्पाद शब्द आउटपुट फ़ंक्शन के साथ वितरित नहीं किया गया है। PLD विकास के पीछे प्रमुख धारणा दोषपूर्ण वायरिंग को हटाकर, एक एकल चिप पर एक यौगिक बूलियन लॉजिक बनाना है, लॉजिक डिज़ाइन से बचना, साथ ही साथ बिजली की खपत को कम करना।

पाल का उदाहरण

निम्नलिखित को लागू करें बूलियन अभिव्यक्ति की मदद से निर्देशयोग्य सरणी तर्क (PAL)

X = AB + AC '

Y = AB '+ BC'

ऊपर दिए गए दो बूलियन कार्य करता है के रूप में हैं SOP (उत्पादों का योग) । बूलियन अभिव्यक्तियों में मौजूद उत्पाद शब्द X & Y हैं, और एक उत्पाद शब्द जो AC है '' प्रत्येक समीकरण में सामान्य है। तो, उपरोक्त दो समीकरण उत्पन्न करने के लिए कुल आवश्यक तर्क गेट्स है और गेट्स -4 या प्रोग्रामेबल गेट्स -2। बराबर PAL तर्क आरेख नीचे दिखाया गया है।

पाल तर्क सर्किट

और गेट जो प्रोग्राम करने योग्य होते हैं, उनमें प्रवेश के लिए सामान्य और साथ ही परिवर्तनीय इनपुट का अधिकार होता है। उपरोक्त तर्क आरेख में, प्रत्येक और गेट के लिए उपलब्ध इनपुट A, A ', B, B', C, C 'हैं। तो, प्रत्येक और गेट के साथ एक एकल उत्पाद शब्द उत्पन्न करने के लिए, कार्यक्रम की आवश्यकता है।

सभी उत्पाद की शर्तें प्रत्येक या गेट के इनपुट पर प्राप्य हैं। यहां, तर्क गेट पर प्रोग्राम योग्य कनेक्शन को प्रतीक 'X' के साथ चिह्नित किया जा सकता है।

यहां, OR गेट इनपुट तय हैं। इस प्रकार, आवश्यक उत्पाद शर्तें प्रत्येक OR गेट इनपुट से जुड़ी होती हैं। नतीजतन, ये द्वार विशेष बूलियन समीकरण उत्पन्न करेंगे। '' प्रतीक स्थायी कनेक्शन का प्रतिनिधित्व करता है।

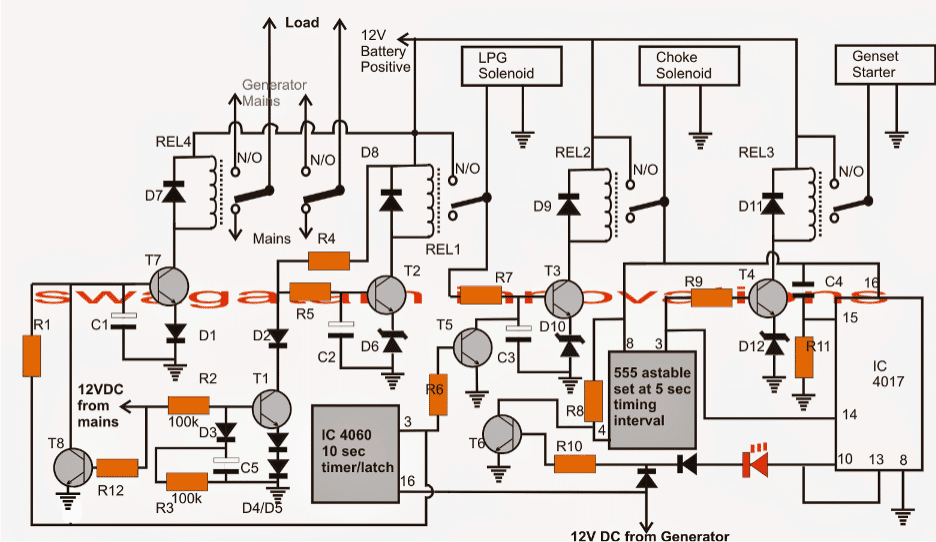

प्रोग्रामेबल तर्क सरणी (पीएलए) का डिजाइन

पीएलए शब्द की परिभाषा बूलियन फ़ंक्शन को उत्पाद की राशि (एसओपी) के रूप में प्रस्तुत करती है। इस प्रोग्रामेबल लॉजिक ऐरे की डिजाइनिंग AND, OR, और नॉट ऑन द चिप पर आधारित लॉकेट का उपयोग करके की जा सकती है, जिससे हर इनपुट के साथ-साथ इसकी तारीफ हर एंड गेट की ओर प्राप्य हो जाती है।

हर OR गेट का आउटपुट हर OR गेट से जुड़ा होता है। अंत में, OR गेट का आउटपुट चिप का आउटपुट उत्पन्न करता है। इस प्रकार, यह है कि उत्पाद के योग के अभिव्यक्तियों का उपयोग करने के लिए एक उपयुक्त संघ कैसे समाप्त होता है। निर्देशयोग्य तर्क सरणी में, AND और OR जैसे तर्क गेट्स के कनेक्शन प्रोग्राम योग्य हैं। पीएलए की तुलना में महंगा और मुश्किल है PAL। PAL दो डिसमिलर विकसित विधियों का उपयोग करता है जिनका उपयोग प्रोग्रामिंग की सहजता को बढ़ाने के लिए प्रोग्रामेबल लॉजिक एरे के लिए किया जा सकता है। इस तरह की विधि में, प्रत्येक कनेक्शन को प्रत्येक चौराहे बिंदु पर फ्यूज का उपयोग करके किया जा सकता है जहां फ्यूज उड़ाने से अनावश्यक कनेक्शनों को अलग किया जा सकता है। अंतिम तकनीक कनेक्शन बनाने की योजना बना रही है, जबकि सटीक इंटरकनेक्शन मॉडल के लिए उपयुक्त कवर का उपयोग करके निर्माण की प्रक्रिया।

पीएलए का उदाहरण

प्रोग्राम तर्क सरणी (PLA) की मदद से निम्नलिखित बूलियन अभिव्यक्ति को लागू करें

X = AB + AC '

Y = AB '+ BC + AC'

ऊपर दिए गए दो बूलियन कार्य एसओपी (उत्पादों की राशि) के रूप में हैं। बूलियन अभिव्यक्तियों में मौजूद उत्पाद शब्द X & Y हैं, और एक उत्पाद शब्द जो AC है '' प्रत्येक समीकरण में सामान्य है। तो, उपरोक्त दो समीकरण उत्पन्न करने के लिए कुल आवश्यक लॉजिक गेट्स है और गेट्स -4, या प्रोग्रामेबल या गेट्स -2। समकक्ष पीएलए तर्क आरेख नीचे दिखाया गया है।

PLA तर्क सर्किट

और गेट जो प्रोग्राम करने योग्य होते हैं, उनमें प्रवेश के लिए सामान्य और साथ ही परिवर्तनीय इनपुट का अधिकार होता है। उपरोक्त तर्क आरेख में, प्रत्येक और गेट के लिए उपलब्ध इनपुट A, A ', B, B', C, C 'हैं। तो, प्रत्येक और गेट के साथ एक एकल उत्पाद शब्द उत्पन्न करने के लिए, कार्यक्रम की आवश्यकता है।

सभी उत्पाद शर्तें प्रत्येक या गेट के इनपुट पर प्राप्य हैं। यहां, तर्क गेट पर प्रोग्राम योग्य कनेक्शन को प्रतीक 'X' के साथ चिह्नित किया जा सकता है।

PAL और PLA के बीच अंतर

टैबुलर फॉर्म में PAL और PLA के बीच अंतर मुख्य रूप से शामिल हैं पाल और पीएलए पूर्ण रूप , निर्माण, उपलब्धता, लचीलापन, लागत, कार्यों की संख्या और गति जो नीचे चर्चा की गई हैं।

| प्रोग्रामेबल ऐरे लॉजिक (पाल) | प्रोग्रामेबल तर्क सरणी (पीएलए) |

| PAL का पूर्ण रूप प्रोग्रामेबल एरे लॉजिक है | पीएलए का पूर्ण रूप एक प्रोग्रामेबल लॉजिक एरे है |

| PAL का निर्माण AND और OR गेट्स के प्रोग्राम संग्रह का उपयोग करके किया जा सकता है | PLA का निर्माण AND और गेट के निश्चित संग्रह के प्रोग्राम संग्रह का उपयोग करके किया जा सकता है। |

| पाल की उपलब्धता कम विपुल है | पीएलए की उपलब्धता अधिक है |

| PAL प्रोग्रामिंग का लचीलापन अधिक है | पीएलए का लचीलापन कम है |

| एक पाल की लागत महंगी है | पीएलए की लागत मध्यम श्रेणी है |

| पाल में कार्यान्वित कार्यों की संख्या बड़ी है | पीएलए में कार्यान्वित कार्यों की संख्या सीमित है |

| PAL की गति धीमी है | पीएलए की गति अधिक है |

इस प्रकार, यह सब PAL और PLA के बारे में है। उपरोक्त जानकारी से, आखिरकार, हम यह निष्कर्ष निकाल सकते हैं कि ये प्रोग्रामेबल लॉजिक डिवाइस (PLDs) हैं जहाँ निर्देशयोग्य तर्क सरणी प्रोग्रामेबल एरे लॉजिक की तुलना में अधिक लचीला है। लेकिन, प्रोग्रामेबल एरे लॉजिक सहजता से कॉम्बिनेशन लॉजिक सर्किट उत्पन्न कर सकता है। यहाँ आपके लिए एक प्रश्न है, की भूमिका क्या है डिजिटल इलेक्ट्रॉनिक्स में पाल और पीएलए ?