एक सही ढंग से गणना की गई MOSFET बारी-बारी प्रक्रिया सुनिश्चित करती है कि डिवाइस को इष्टतम दक्षता के साथ चालू किया गया है।

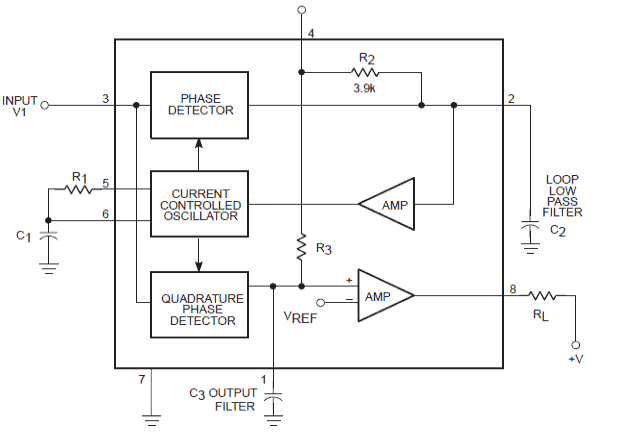

MOSFET आधारित सर्किट डिजाइन करते समय आपने सोचा होगा कि MOSFET को चालू करने का सही तरीका क्या है? या बस न्यूनतम वोल्टेज क्या है जो इसे पूरी तरह से चालू करने के लिए गेट / डिवाइस के स्रोत पर लागू किया जाना चाहिए?

हालांकि कई डिजिटल सिस्टम के लिए यह एक मुद्दा नहीं हो सकता है, 5V सिस्टम जैसे DSP, FPGAs और Arduinos की आवश्यकता है उनके आउटपुट को बढ़ावा देना जुड़े MOSFET के लिए इष्टतम स्विचिंग की स्थिति के लिए।

और इन स्थितियों में डिजाइनर थ्रेशोल्ड वोल्टेज डेटा प्राप्त करने के लिए MOSFET के विनिर्देशों को देखना शुरू कर देता है। डिज़ाइनर मानता है कि MOSFET चालू हो जाएगा और इस थ्रेशोल्ड स्तर को पार करने पर स्थिति बदल जाएगी।

हालाँकि यह उतना सरल नहीं हो सकता है जितना यह प्रतीत हो सकता है।

थ्रेशोल्ड वोल्टेज V क्या हैजीएस (वें)

सबसे पहले हमें एहसास होना चाहिए कि दहलीज वोल्टेज, वी के रूप में चिह्नित हैजीएस (वें)सर्किट डिजाइनरों के बारे में चिंता करने के लिए नहीं है।

सटीक होने के लिए, यह गेट वोल्टेज है जो MOSFET के ड्रेन करंट को 250 μA के थ्रेसहोल्ड स्तर को पार करने का कारण बनता है, और यह उन परिस्थितियों में परीक्षण किया जाता है, जो व्यावहारिक अनुप्रयोगों में सामान्य रूप से ट्रांसपायर नहीं हो सकते हैं।

कुछ विश्लेषण के दौरान, डिवाइस के उपर्युक्त परीक्षण के लिए एक निरंतर 5V का उपयोग किया जाता है। लेकिन यह परीक्षण आम तौर पर गेट से जुड़ा हुआ है और डिवाइस की नाली एक दूसरे के साथ जुड़ी या छोटी है। आप इस जानकारी को डेटाशीट में आसानी से प्राप्त कर सकते हैं, इसलिए इस परीक्षण के बारे में कुछ भी रहस्यमय नहीं है।

ऊपर दी गई तालिका दहलीज के स्तर और एक उदाहरण MOSFET के लिए प्रासंगिक परीक्षण स्थितियों को इंगित करती है।

एक वांछित एप्लिकेशन के लिए डिज़ाइनर 'प्रेरित' गेट वोल्टेज के रूप में जानी जाने वाली खतरनाक स्थिति के बारे में चिंतित हो सकता है, जो कम पक्ष में उदाहरण के लिए एक गंभीर मुद्दा हो सकता है MOSFET तुल्यकालिक हिरन कनवर्टर ।

जैसा कि पहले चर्चा की गई थी, यहां भी हमें यह समझना चाहिए कि दहलीज को पार करते हुए वीजीएस (वें)स्तर उपकरण को शूट-थ्रू ब्रेकडाउन स्थिति में चलाने के लिए मजबूर नहीं कर सकता है। यह स्तर वास्तव में डिजाइनर को उस दहलीज के बारे में बताता है जिस पर MOSFET बस चालू करना शुरू करता है और ऐसी स्थिति नहीं है जहां चीजें पूरी तरह से समाप्त हो जाती हैं।

यह सलाह दी जा सकती है कि जब MOSFET स्विच ऑफ स्थिति में हो तो गेट वोल्टेज V के नीचे बनाए रखा जाता हैजीएस (वें)स्तर, वर्तमान रिसाव को रोकने के लिए। लेकिन इसे चालू करते समय इस पैरामीटर को केवल अनदेखा किया जा सकता है।

विशेषता वक्र स्थानांतरण

आपको एक और वक्र आरेख नाम दिया जाएगा स्थानांतरण विशेषताओं MOSFET डेटाशीट्स में गेट वोल्टेज बढ़ाने के जवाब में व्यवहार पर अपनी बारी की व्याख्या करते हुए।

सटीक होने के लिए यह गेट वोल्टेज और डिवाइस केस तापमान के संबंध में वर्तमान भिन्नता विश्लेषण से अधिक संबंधित हो सकता है। इस विश्लेषण में वीडी एस15V के आसपास एक निश्चित स्तर पर उच्च स्तर पर आयोजित किया जाता है, जो डेटाशीट स्पेक्स में प्रकट नहीं हो सकता है।

अगर हम ऊपर दिखाए गए वक्र को देखें तो हमें पता चलता है कि 20 एम्पी ड्रेन करंट के लिए, 3.2 V गेट-टू-सोर्स वोल्टेज पर्याप्त नहीं हो सकता है।

संयोजन 10 V के VDS में आमतौर पर 200 वाट के अपव्यय के साथ होता है।

स्थानांतरण वक्र डेटा रैखिक सीमा में संचालित MOSFETs के लिए उपयोगी हो सकता है, हालांकि स्विचिंग अनुप्रयोगों में MOSFETs के लिए वक्र डेटा का कम महत्व हो सकता है।

आउटपुट विशेषताएँ

वक्र जो MOSFET की पूरी तरह चालू स्थिति के बारे में वास्तविक डेटा का खुलासा करता है, उसे नीचे दिखाए गए आउटपुट वक्र के रूप में जाना जाता है:

यहां, वी के विभिन्न स्तरों के लिएजी एसMOSFET की आगे की बूंद को करंट के फंक्शन के रूप में मापा जाता है। गेट वोल्टेज के इष्टतम स्तर की पुष्टि करने के लिए डिवाइस इंजीनियर इस वक्र डेटा का उपयोग करते हैं।

गेट वोल्टेज के प्रत्येक स्तर के लिए जो MOSFET [R] का पूर्ण स्विच ऑन सुनिश्चित करता हैडीएस (पर)], हमें वोल्टेज ड्रॉप (वी) की एक श्रृंखला मिलती हैजी एस) ड्रेन-टू-सोर्स के साथ ड्रेन करंट के साथ सख्ती से रैखिक प्रतिक्रिया। सीमा शून्य और ऊपर से शुरू होती है।

निचले गेट वोल्टेज के लिए (वीजी एस), जब नाली की धारा बढ़ जाती है, तो हम वक्र को रैखिक प्रतिक्रिया खोते हुए पाते हैं, जो 'घुटने' से होकर चलती है और फिर सपाट होती है।

उपरोक्त वक्र विवरण हमें 2.5 वी से 3.6 वी तक गेट वोल्टेज की एक श्रृंखला के लिए पूर्ण आउटपुट विशेषताएँ प्रदान करते हैं।

MOSFET उपयोगकर्ता आमतौर पर इसे रैखिक फ़ंक्शन के रूप में मनन कर सकते हैं। हालांकि, इसके विपरीत डिवाइस इंजीनियर ग्राफ़ के ग्रे क्षेत्र की ओर अधिक ध्यान देना पसंद कर सकते हैं जो लागू गेट वोल्टेज के लिए वर्तमान संतृप्ति क्षेत्र का सुझाव देता है।

यह वर्तमान डेटा को दर्शाता है जिसने संतृप्ति बिंदु या संतृप्ति सीमा को छू लिया है। इस बिंदु पर, यदि वीडी एसवृद्धि से करंट में मामूली बढ़ोतरी होगी, लेकिन ड्रेन करंट में थोड़ी वृद्धि से बहुत बड़ा V हो सकता हैडी एस।

बढ़े हुए वोल्टेज स्तर के लिए, जो MOSFET को पूरी तरह से चालू करने में सक्षम बनाता है, हरे रंग का छायांकित क्षेत्र हमें प्रक्रिया के लिए ऑपरेटिंग बिंदु दिखाएगा, जिसे प्रतिरोधक (या ओमिक) क्षेत्र के रूप में दर्शाया गया है।

कृपया ध्यान दें कि यहाँ घटता केवल विशिष्ट मान दिखाता है, और इसमें कोई न्यूनतम या अधिकतम सीमा शामिल नहीं है।

कम परिवेश के तापमान पर काम करते समय, डिवाइस को प्रतिरोधक क्षेत्र में रहने के लिए उच्च गेट वोल्टेज की आवश्यकता होगी, जो 0.3% / ° C की दर से ऊपर जा सकता है।

MOSFET RDS क्या है (पर)

जब डिवाइस इंजीनियरों को MOSFET की आउटपुट विशेषताओं का सामना करना पड़ता है, तो वे अनिवार्य रूप से आर के बारे में सीखना चाहेंगेडीएस (पर)डिवाइस के विशिष्ट ऑपरेटिंग परिस्थितियों के संदर्भ में।

आम तौर पर, यह वी का मिश्रण हो सकता हैजी एसऔर मैंडी एसउस क्षेत्र में जहां वक्र सीधी रेखा से ग्रे शेड द्वारा इंगित भाग में विचलित हो गया है।

ऊपर चर्चा किए गए उदाहरण को ध्यान में रखते हुए, 10 वीपीएस के प्रारंभिक वर्तमान के साथ 3.1 वी का एक गेट वोल्टेज, इंजीनियरों को पता चल जाएगा कि आर।डीएस (पर)अनुमानित मूल्य से अधिक होगा। यह कहने के बाद, क्या हम MOSFET निर्माता से इस बारे में अनुमानित डेटा प्रस्तुत करने की उम्मीद करते हैं?

दोनों राशियों के साथ वीडी एसऔर मैंडी एसवक्र में आसानी से प्राप्य यह बहुत मोहक बन सकता है, और अक्सर परिणामी आर में दो मात्राओं को विभाजित करने के लिए आत्मसमर्पण किया जाता हैडीएस (पर)।

हालांकि, दुख की बात है कि हमारे पास एक आर नहीं हैडीएस (पर)यहाँ मूल्यांकन के लिए। यह उल्लिखित स्थितियों के लिए अनुपलब्ध लगता है क्योंकि किसी भी अनुभाग के लिए घाट एक प्रतिरोध का प्रतिनिधित्व एक रैखिक तरीके से मूल के माध्यम से पार करना है।

इसने कहा, भार रेखा को एक गैर-रेखीय प्रतिरोध की तरह समग्र रूप में अनुकरण करना संभव हो सकता है।

न्यूनतम पर, यह गारंटी देगा कि व्यावहारिक कार्य की कोई भी समझ मूल (0, 0) पर बनी हुई है।

गेट चार्ज वक्र लक्षण

यह गेट चार्ज वक्र डेटा है जो वास्तव में हमें MOSFET के बारी बारी से संबंधित वास्तविक संकेत देता है जैसा कि नीचे दिए गए चित्र में दिखाया गया है :

यद्यपि उपरोक्त वक्र सभी MOSFET डेटाशीट में एक मानक समावेश है, अंतर्निहित संकेत MOSFET उपयोगकर्ता द्वारा शायद ही कभी संकलित किए जाते हैं।

इसके अलावा, MOSFET लेआउट में आधुनिक उन्नति, जैसे खाई और परिरक्षित द्वार, डेटा के संशोधित पते के लिए कॉल करते हैं।

उदाहरण के लिए, 'गेट-चार्ज' नाम का विनिर्देश स्वयं ही थोड़ा भ्रामक दिखाई दे सकता है।

वक्र के रैखिक और विभाजित खंड वोल्टेज संधारित्र को चार्ज करने की तरह दिखाई नहीं देते हैं, भले ही यह गैर-रैखिक मूल्य कितना भी प्रदर्शित हो।

सटीक होने के लिए, गेट चार्ज वक्र दो गैर समानांतर कैपेसिटर के एक संबद्ध डेटा को दर्शाता है, जिसमें असमान परिमाण होता है और विभिन्न वोल्टेज स्तर होते हैं।

सिद्धांत रूप में, MOSFET गेट टर्मिनल से देखे गए कार्यात्मक समाई को समीकरण के साथ परिभाषित किया गया है:

सीआईएसएस= सीजी एस+ सीगोलों का अंतर

जहां सीआईएसएस= गेट कैपेसिटेंस, सीजी एस= गेट सोर्स कैपेसिटी, सीगोलों का अंतर= गेट ड्रेन कैपेसिटी

यद्यपि यह इस इकाई को मापने के लिए और डेटाशीट में निर्दिष्ट करने के बजाय सरल दिखाई दे सकता है, यह ध्यान दिया जाना चाहिए कि शब्द सीआईएसएसवास्तव में एक वास्तविक समाई नहीं है।

यह सोचना पूरी तरह से गलत हो सकता है कि MOSFET को केवल 'गेट कैपेसिटेंस C' पर लगाए गए वोल्टेज के माध्यम से चालू किया जाता हैआईएसएस'।

जैसा कि उपरोक्त आंकड़े में बताया गया है, एक MOFET चालू होने से पहले, गेट कैपेसिटेंस पर कोई चार्ज नहीं है, लेकिन गेट-ड्रेन C पर कैपेसिटेंसगोलों का अंतरएक नकारात्मक चार्ज रखता है जिसे समाप्त करने की आवश्यकता है।

इन दोनों समाई में गैर-रेखीय प्रकृति होती है और उनके मान काफी हद तक भिन्न होते हैं क्योंकि लागू वोल्टेज अलग-अलग होते हैं।

इसलिए, यह ध्यान रखना महत्वपूर्ण है कि यह MOSFET का संग्रहीत शुल्क है जो इसकी स्विचिंग विशेषताओं को निर्धारित करता है, न कि किसी विशिष्ट वोल्टेज स्तर के लिए समाई मान।

चूंकि दो समाई तत्व सी का निर्माण करते हैंआईएसएसअलग-अलग भौतिक गुण होते हैं, वे असमान वोल्टेज स्तरों के साथ चार्ज होने लगते हैं, MOSFET की प्रक्रिया को भी दो चरणों से गुजरने की आवश्यकता होती है।

प्रतिरोधक और आगमनात्मक अनुप्रयोगों के लिए सटीक अनुक्रम भिन्न हो सकता है, लेकिन आमतौर पर अधिकांश व्यावहारिक भार अत्यधिक प्रेरक होते हैं, इस प्रक्रिया को निम्नलिखित आकृति में दर्शाया गया है:

गेट चार्ज टाइमिंग सीक्वेंस

MOSFET के गेट चार्ज टाइमिंग क्रम का अध्ययन नीचे दिए गए आरेख से किया जा सकता है:

इसे निम्नलिखित स्पष्टीकरण के साथ समझा जा सकता है:

- टी 0 - टी 1: सीजी एसशून्य से V तक के शुल्कजीएस (वें)... वीडी एसया मैंडी एसकिसी भी परिवर्तन के माध्यम से नहीं जाता है।

- T1-T2, V से बढ़ते गेट वोल्टेज के जवाब में MOSFET में करंट बढ़ने लगता हैजीएस (वें)पठार वोल्टेज V तकजीपी।

- यहां, आईडीएस बढ़ता है और 0 वी से पूर्ण लोड वर्तमान तक पहुंचता है, हालांकि वीडी एसअप्रभावित और स्थिर रहता है। संबद्ध चार्ज C के इंटीग्रल के माध्यम से बनता हैजी एस0 वी से वी तकजीपी, और क्यूजी एसडेटशीट में दिया गया।

- T2 - T3: T2 और T3 के बीच समतल क्षेत्र का निरीक्षण करें, इसे मिलर पठार कहा जाता है।

- स्विच ऑन करने से पहले, सीगोलों का अंतरप्रभार और आपूर्ति वोल्टेज V तक रखती हैमें, जब तक मैंडी एसT2 पर चरम मान I (लोड) तक पहुंचता है।

- अवधि T2 और T3 के बीच का समय, नकारात्मक आवेश (V)में- वीजीपी) पठार वोल्टेज V के संबंध में धनात्मक आवेश में परिवर्तित हो जाता हैजीपी।

- यह वी से नाली वोल्टेज के गिरने के रूप में भी कल्पना की जा सकती हैमेंलगभग शून्य तक।

- इसमें शामिल चार्ज सी के आसपास के बराबर हैगोलों का अंतर0 से V तक अभिन्नमें, जो क्यू के रूप में दिखाया गया हैगोलों का अंतरडेटशीट में।

- T3 - T4 के दौरान, गेट वोल्टेज V से चढ़ता हैजीपीसे V तकजी एस, और यहाँ हम वी के लिए शायद ही कोई बदलाव पाते हैंडी एसऔर मैंडी एस, लेकिन प्रभावशाली आरडीएस (पर)गेट वोल्टेज के बढ़ने पर थोड़ा गिरता है। वी के ऊपर कुछ वोल्टेज स्तर परजीपी, प्रभावी आर पर ऊपरी सीमा को ठीक करने के लिए पर्याप्त आत्मविश्वास प्रदान करता हैडीएस (पर)।

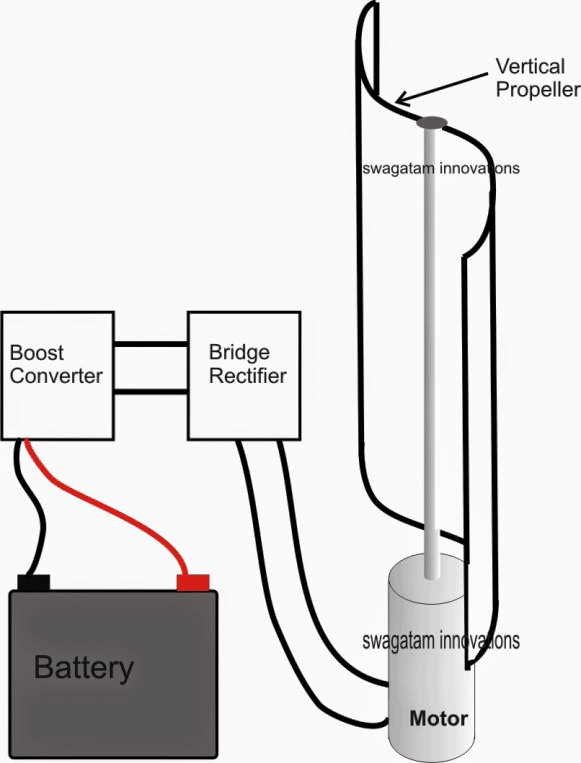

आगमनात्मक भार के लिए

वोल्टेज गिरने से पहले एक आगमनात्मक लोड की आवश्यकता के कारण MOSFET चैनल में वर्तमान का उदय।

पठार के प्रारंभ में, MOSFET, ऑफ स्टेट में है, एक उच्च धारा और वोल्टेज से लेकर स्रोत तक मौजूद है।

T2 और T3 के समय के बीच, एक आवेश Qगोलों का अंतरMOSFET के गेट पर लागू किया जाता है, जिसमें MOSFET विशेषता अंत में निरंतर वर्तमान से निरंतर प्रतिरोध मोड में बदल जाती है।

जब उपरोक्त संक्रमण होता है, तो गेट वोल्टेज वी में कोई ध्यान देने योग्य परिवर्तन नहीं होता हैजीपीजगह लेता है।

यही कारण है कि गेट वोल्टेज के किसी भी विशेष स्तर के साथ MOSFET टर्न ओन प्रक्रिया से संबंधित एक बुद्धिमान विचार कभी नहीं है।

स्विच ऑफ प्रक्रिया के लिए भी यही सही हो सकता है, जो विपरीत क्रम में MOSFET के गेट से समान दो शुल्क (पहले चर्चा की गई) को समाप्त करने की मांग करता है।

MOSFET स्विचिंग गति

जबकि क्यूजी एसप्लस क्यूगोलों का अंतरएक साथ यह सुनिश्चित करता है कि MOSFET पूरी तरह से चालू हो जाएगा, यह हमें नहीं बताता कि यह कितनी जल्दी होगा।

वर्तमान या वोल्टेज कितनी तेजी से स्विच करेगा यह उस दर से तय किया जाता है जिसके माध्यम से गेट पर चार्ज तत्व लागू होते हैं या हटा दिए जाते हैं। इसे गेट ड्राइव करंट भी कहा जाता है।

यद्यपि तेजी से वृद्धि और गिरावट की दर MOSFETs में कम स्विचिंग घाटे को सुनिश्चित करती है, ये विशेष रूप से वृद्धि की पीक वोल्टेज, दोलनों और विद्युत चुम्बकीय हस्तक्षेप से संबंधित प्रणाली स्तर की जटिलताओं को जन्म दे सकती है, विशेष रूप से प्रेरक भार के टर्न ऑफ इंस्टेंट के दौरान।

उपरोक्त Fig.7 में दर्शाया गया रैखिक रूप से गिरने वाला वोल्टेज Cgd का एक निरंतर मूल्य लेने का प्रबंधन करता है, जो कि व्यावहारिक अनुप्रयोगों में MOSFETs के लिए शायद ही हो सकता है।

सटीक होने के लिए, गेट-ड्रेन चार्ज सीगोलों का अंतरएक उच्च वोल्टेज सुपर जंक्शन MOSFET के लिए जैसे कि SiHF35N60E एक काफी उच्च रैखिक प्रतिक्रिया प्रदर्शित करता है, जैसा कि निम्नलिखित आंकड़ा देखा जा सकता है:

भिन्नता सीमा जो C के मान में मौजूद हैआरएसएस(रिवर्स ट्रांसफर) प्रारंभिक 100 V के भीतर 200: 1 से अधिक है। इसके कारण गेट चार्ज वक्र के खिलाफ वोल्टेज का वास्तविक गिरावट समय आंकड़ा 7 में लाल रंग में दिखाई गई धराशायी लाइन की तरह अधिक दिखाई देता है।

उच्च उतार-चढ़ाव पर, शुल्कों के बढ़ने और गिरने के समय के साथ-साथ उनके बराबर dV / dt मान C के मान पर अधिक निर्भर होते हैंआरएसएसइसके बजाय क्यू के रूप में इंगित पूरे वक्र के अभिन्न अंग के रूप मेंगोलों का अंतर।

जब उपयोगकर्ता विभिन्न डिज़ाइन वातावरण के भीतर MOSFET चश्मा की तुलना करना चाहते हैं, तो उन्हें यह महसूस करना चाहिए कि MOSFET आधे Q के साथ हैगोलों का अंतरमूल्य जरूरी दो बार तेजी से स्विचिंग दर, या 50% कम स्विचिंग नुकसान की सुविधा नहीं देगा।

ऐसा इसलिए है, क्योंकि C के अनुसारगोलों का अंतरउच्च वोल्टेज पर वक्र और इसकी परिमाण, MOSFET के लिए डेटाशीट में कम Qgd होना काफी संभव हो सकता है, लेकिन स्विचिंग गति में कोई वृद्धि के बिना।

सारांश

वास्तविक कार्यान्वयन में, MOSFET का टर्निंग ऑन प्रक्रियाओं की एक श्रृंखला के माध्यम से होता है, न कि पूर्व निर्धारित पैरामीटर के साथ।

सर्किट डिजाइनरों को उस वी की कल्पना करना बंद कर देना चाहिएजीएस (वें), या वोल्टेज का स्तर MOSFET आउटपुट को उच्च से निम्न R पर स्विच करने के लिए गेट वोल्टेज के रूप में उपयोग किया जा सकता हैडीएस (पर)।

आर होने के बारे में सोचना निरर्थक हो सकता हैडीएस (पर)एक विशिष्ट गेट वोल्टेज स्तर के नीचे या ऊपर, चूंकि गेट वोल्टेज स्तर आंतरिक रूप से किसी MOSFET के मोड़ को तय नहीं करता है। बल्कि यह आरोप क्यू हैजी एसऔर क्यूगोलों का अंतरMOSFET में पेश किया गया जो नौकरी को अंजाम देता है।

आपको V से ऊपर उठने वाला गेट वोल्टेज मिल सकता हैजीएस (वें)और वीजीपीचार्ज / डिस्चार्ज प्रक्रिया के दौरान लेकिन ये इतने महत्वपूर्ण नहीं हैं।

इसी तरह, MOSFET आज कितनी तेजी से चालू हो सकता है या बंद क्यू का एक जटिल कार्य हो सकता हैजी एसया क्यूगोलों का अंतर।

MOSFET स्विचिंग गति, विशेष रूप से उन्नत MOSFETs के मूल्यांकन के लिए, डिजाइनर को गेट चार्ज वक्र और डिवाइस की कैपेसिटेंस विशेषता के बारे में एक व्यापक अध्ययन से गुजरना होगा।

संदर्भ: https://www.vishay.com/

की एक जोड़ी: स्थानांतरण विशेषताओं अगला: TL494 डेटाशीट, पिनआउट, एप्लिकेशन सर्किट