इस पोस्ट में हम MOSFET हिमस्खलन रेटिंग्स पर चर्चा करते हैं, और यह सीखते हैं कि डेटासेट में इस रेटिंग को कैसे ठीक से समझा जाए, निर्माता द्वारा परीक्षण कैसे किया जाता है, और इस घटना से MOSFETs की सुरक्षा के उपाय।

हिमस्खलन पैरामीटर न केवल उपकरणों के बीहड़पन को सत्यापित करने में मदद करता है, यह अतिरिक्त रूप से कमजोर MOSFETs या उन लोगों को छानने में मदद करता है जो अधिक अतिसंवेदनशील या टूटने के जोखिम में हैं।

MOSFET हिमस्खलन रेटिंग क्या है

MOSFET हिमस्खलन रेटिंग एक अधिकतम सहनशील ऊर्जा (मिलीजुएल) है जो एक MOSFET झेल सकता है, जब इसकी नाली-स्रोत वोल्टेज अधिकतम टूटने वाली वोल्टेज (BVDSS) की सीमा से अधिक हो जाती है।

यह घटना सामान्य रूप से MOSFET स्विचिंग सर्किट में ड्रेन टर्मिनल पर आगमनात्मक भार के साथ होती है।

स्विचिंग चक्रों की अवधि के दौरान, प्रारंभ करनेवाला शुल्क, और ऑफ अवधि के दौरान प्रारंभ करनेवाला MOSFET के स्रोत-नाली में वापस EMF के रूप में अपनी संग्रहीत ऊर्जा जारी करता है।

यह रिवर्स वोल्टेज MOSFET के बॉडी डायोड के माध्यम से अपना रास्ता ढूंढता है, और यदि इसका मान डिवाइस की अधिकतम सहनीय सीमा से अधिक हो जाता है, तो डिवाइस के भीतर तीव्र गर्मी विकसित होती है जिससे डिवाइस को नुकसान या स्थायी नुकसान होता है।

जब MOSFET हिमस्खलन का परिचय दिया गया था

अवाल्चे एनर्जी और यूआईएस (अप्रभावित आगमनात्मक स्विचिंग) का पैरामीटर, वास्तव में 1980 के दशक से पहले MOSFET डेटाशीट में शामिल नहीं था।

और ऐसा तब है जब यह न केवल डेटशीट विनिर्देश में विकसित हुआ, बल्कि एक पैरामीटर जो कई उपभोक्ताओं की मांग थी कि उत्पादन के लिए डिवाइस पास करने से पहले एफईटी का परीक्षण किया जाए, खासकर, अगर एमओएसएफईटी को बिजली की आपूर्ति या स्विचिंग कार्यान्वयन के लिए डिज़ाइन किया जा रहा है।

इसलिए यह 1980 के दशक के बाद से ही एवलांश पैरामीटर डेटाशीट्स में दिखाई देने लगा था, और फिर प्रमोशन तकनीशियनों ने यह समझना शुरू कर दिया कि एवलांच रेटिंग जितनी बड़ी थी, उतना ही अधिक प्रतिस्पर्धी उपकरण दिखाई दिया।

इंजीनियरों ने इसके कुछ चरों को मोड़कर पैरामीटर के साथ प्रयोग करने के लिए तकनीकों का निर्धारण शुरू किया, जो परीक्षण प्रक्रिया के लिए उपयोग किए गए थे।

सामान्यतया, हिमस्खलन ऊर्जा जितनी बड़ी होती है, MOSFET उतना ही अधिक टिकाऊ और मजबूत होता है। इसलिए बड़ा हिमस्खलन रेटिंग, मजबूत MOSFET विशेषताओं का प्रतिनिधित्व करता है।

अधिकांश एफईटी डेटशीट में उनके निरपेक्ष अधिकतम रेटिंग तालिका में शामिल हिमस्खलन पैरामीटर होगा, जो सीधे डेटा शीट के प्रवेश पृष्ठ पर पाया जा सकता है। विशेष रूप से, आप यहाँ लिखे मापदंडों को हिमस्खलन करंट और हिमस्खलन ऊर्जा, आसान के रूप में देख सकते हैं।

इसलिए, डेटशीट में MOSFET हिमस्खलन ऊर्जा को ऊर्जा की मात्रा के रूप में प्रस्तुत किया जाता है MOSFET को सहन करने में सक्षम है, जबकि यह हिमस्खलन परीक्षण के अधीन है, या जब MOSFET की अधिकतम ब्रेकडाउन वोल्टेज रेटिंग पार की जाती है।

हिमस्खलन करंट और यूआईएस

यह अधिकतम ब्रेकडाउन वोल्टेज रेटिंग एवलांच करंट टेस्ट के माध्यम से निर्धारित की जाती है, जो एक अनक्लेम्पड इंडक्टिव स्विचिंग टेस्ट या यूआईएस टेस्ट के माध्यम से पूरा किया जाता है।

इसलिए जब इंजीनियर UIS करंट के बारे में चर्चा करते हैं, तो वे हिमस्खलन करंट का जिक्र कर सकते हैं।

एक अस्पष्ट Inductive स्विचिंग परीक्षण वर्तमान का पता लगाने के लिए किया जाता है और इस प्रकार हिमस्खलन ऊर्जा जो MOSFET विफलता को ट्रिगर कर सकती है।

जैसा कि पहले उल्लेख किया गया है, ये परिमाण या रेटिंग परीक्षण विनिर्देशों पर विशेष रूप से निर्भर हैं, विशेष रूप से, परीक्षण के समय लागू किए गए प्रारंभ करनेवाला मान।

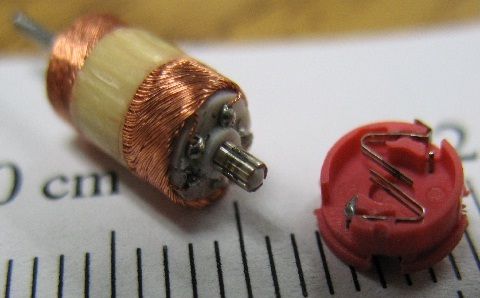

परीक्षण व्यवस्था

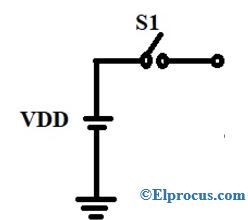

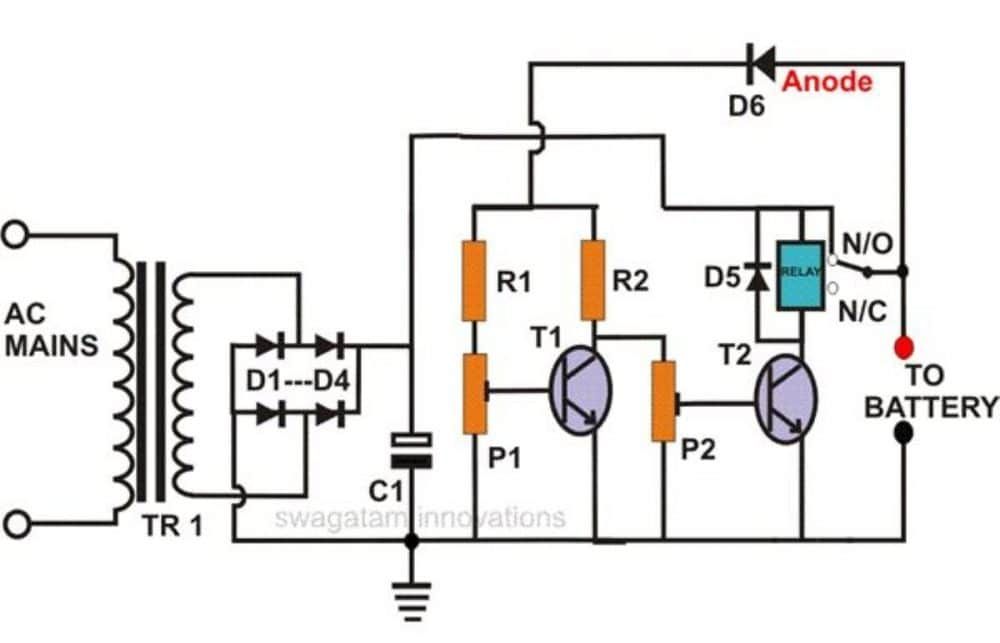

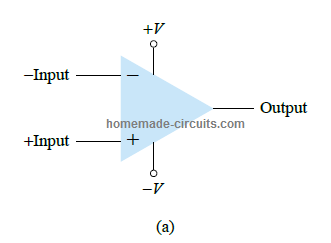

निम्न आरेख एक मानक यूआईएस परीक्षण सर्किट सेट अप दिखाता है।

इस प्रकार हम एक प्रारंभ करनेवाला, एल के साथ श्रृंखला में एक वोल्टेज की आपूर्ति देखते हैं, जो परीक्षण के तहत MOSFET के साथ श्रृंखला में भी है। हम FET के लिए एक गेट ड्राइवर भी देख सकते हैं जिसका आउटपुट FET गेट रेसिस्टेंट R के साथ श्रृंखला में है।

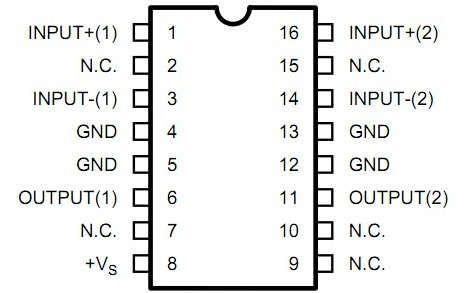

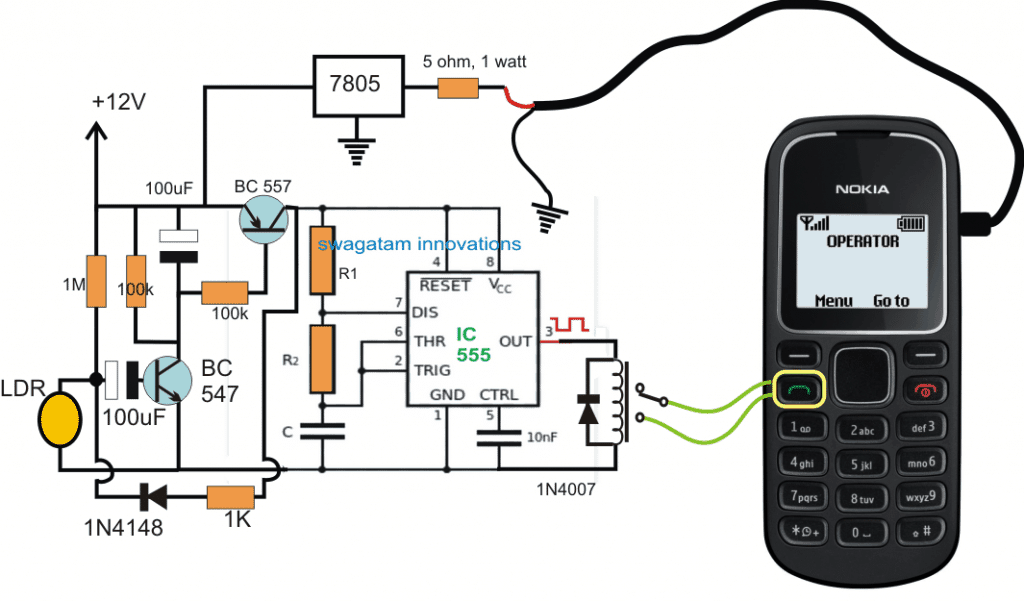

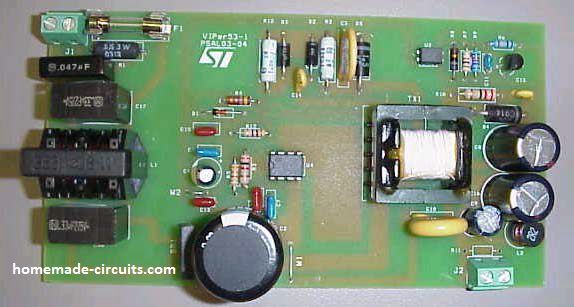

नीचे की छवि में, हम पाते हैं, LTC55140 नियंत्रक डिवाइस, जिसका उपयोग टेक्सास इंस्ट्रूमेंट लैब में एफईटी की यूआईएस विशेषताओं का मूल्यांकन करने के लिए किया जाता है।

बाद में यूआईएस विशेषता न केवल एफईटी डेटशीट रेटिंग का पता लगाने में मदद करती है, बल्कि अंतिम परीक्षण प्रक्रिया में एफईटी को स्कैन करने के लिए उपयोग किए जाने वाले मूल्य का भी।

उपकरण 0.2 से 160 मिलीयन तक लोड प्रारंभ करनेवाला मान को ट्विक करने की अनुमति देता है। यह 10 से 150 वोल्ट से परीक्षण के तहत MOSFET के नाली वोल्टेज के समायोजन की अनुमति देता है।

परिणामस्वरूप, यह उन FET को भी स्क्रीन करना संभव बनाता है जो केवल 100 वोल्ट ब्रेकडाउन वोल्टेज को संभालने के लिए रेटेड हैं। और, यह संभव हो जाता है कि 0.1 से 200 एम्पियर तक ड्रेन धाराएं लगाई जाएं। और यह यूआईएस वर्तमान सीमा है जिसे एफईटी को परीक्षण प्रक्रिया के दौरान सहन करना पड़ सकता है।

इसके अतिरिक्त टूल MOSFET केस तापमान की विभिन्न श्रेणियों को -55 से +150 डिग्री तक सेट करने की अनुमति देता है।

परीक्षण की प्रक्रिया

मानक यूआईएस परीक्षण 4 चरणों के माध्यम से कार्यान्वित किया जाता है, जैसा कि निम्नलिखित छवि में दिखाया गया है:

पहले चरण में प्री-लीकेज टेस्ट होता है, जिसमें आपूर्ति वोल्टेज एफईटी ड्रेन को बायसेप्ट करता है। मौलिक रूप से, FET को सामान्य अपेक्षित तरीके से निष्पादित करने के लिए सुनिश्चित करने के लिए यहाँ विचार है।

इस प्रकार, पहले चरण में FET को बंद रखा जाता है। यह डेम-एमिटर टर्मिनलों के पार आपूर्ति वोल्टेज को अवरुद्ध रखता है, इसके माध्यम से किसी भी तरह के अत्यधिक रिसाव के प्रवाह का अनुभव नहीं होता है।

दूसरे चरण में, जिसे हिमस्खलन करंट रैंप के रूप में जाना जाता है, एफईटी को चालू किया जाता है, जिससे इसकी नाली वोल्टेज गिरती है। यह वर्तमान में एक निरंतर di / dt के साथ प्रारंभ करनेवाला के माध्यम से धीरे-धीरे बढ़ाने के लिए परिणाम है। तो मूल रूप से इस चरण में, प्रारंभ करने वाले को चार्ज करने की अनुमति दी जाती है।

तीसरे चरण में, वास्तविक हिमस्खलन परीक्षण किया जाता है, जहां एफईटी व्यावहारिक रूप से हिमस्खलन के अधीन होता है। इस चरण में FET को उसके गेट पूर्वाग्रह को हटाकर बंद कर दिया जाता है। यह एक बड़े पैमाने पर di / डीटी में प्रारंभ करनेवाला के माध्यम से प्राप्त होता है, जिससे FET नाली वोल्टेज FET के ब्रेकडाउन वोल्टेज सीमा से ऊपर उच्च गोली मारता है।

यह FET को हिमस्खलन वृद्धि से गुजरने के लिए मजबूर करता है। इस प्रक्रिया में, FET, प्रारंभ करनेवाला द्वारा उत्पन्न पूरी ऊर्जा को अवशोषित करता है, और जब तक 4 वाँ चरण निष्पादित नहीं हो जाता है, तब तक पोस्ट रिसाव परीक्षण शामिल रहता है, बंद रहता है

इस 4 वें चरण में FET को एक बार फिर से दोहराए जाने वाले हिमस्खलन परीक्षण के अधीन किया गया है, बस यह सुनिश्चित करने के लिए कि क्या MOSFET अभी भी सामान्य रूप से व्यवहार कर रहा है या नहीं। यदि ऐसा होता है, तो FET को हिमस्खलन की परीक्षा उत्तीर्ण माना जाता है।

इसके बाद, एफईटी को कई बार उपरोक्त परीक्षा से गुजरना पड़ता है, जिसमें यूआईएस वोल्टेज स्तर धीरे-धीरे प्रत्येक परीक्षण के साथ बढ़ जाता है, जब तक कि एमओएसएफईटी उस स्तर का सामना करने में असमर्थ और रिसाव-रिसाव परीक्षण में विफल रहता है। और इस मौजूदा स्तर को MOSFET की अधिकतम यूआईएस वर्तमान क्षमता के रूप में जाना जाता है।

MOSFET हिमस्खलन ऊर्जा की गणना

एक बार MOSFET की अधिकतम यूआईएस वर्तमान हैंडलिंग क्षमता का एहसास हो जाता है, जिस पर उपकरण टूट जाता है, इंजीनियरों के लिए हिमस्खलन प्रक्रिया के दौरान एफईटी के माध्यम से ऊर्जा का प्रसार करने की मात्रा का अनुमान लगाना बहुत आसान हो जाता है।

यह मानते हुए कि प्रारंभ करनेवाला में संग्रहीत पूरी ऊर्जा को हिमस्खलन के दौरान MOSFET में विसर्जित कर दिया गया था, इस ऊर्जा परिमाण को निम्न सूत्र का उपयोग करके निर्धारित किया जा सकता है:

हैजैसा= 1 / 2L x Iकादो

हैजैसाहमें ऊर्जा को परिचालक के अंदर संग्रहित करने की शक्ति प्रदान करता है, जो प्रारंभ में प्रवाहित प्रवाह से प्रवाहित मूल्य के 50% के बराबर है।

इसके अलावा, यह देखा गया कि प्रारंभ करनेवाला मूल्य में वृद्धि के रूप में, MOSFET टूटने के लिए जिम्मेदार वर्तमान की मात्रा वास्तव में कम हो गई थी।

हालाँकि यह वास्तव में प्रारंभ करनेवाला आकार में वृद्धि को इस ऊर्जा में वर्तमान में उपरोक्त ऊर्जा सूत्र में इस तरह से कम कर देता है कि ऊर्जा का मूल्य सचमुच बढ़ जाता है।

हिमस्खलन ऊर्जा या हिमस्खलन वर्तमान?

ये दो पैरामीटर हैं, जो उपभोक्ताओं को भ्रमित कर सकते हैं, जबकि हिमस्खलन रेटिंग के लिए MOSFET डेटाशीट की जांच कर सकते हैं।

कॉपीराइट © टेक्सास इंस्ट्रूमेंट्स शामिल

MOSFET निर्माताओं में से कई जानबूझकर MOSFET का परीक्षण बड़े प्रेरकों के साथ करते हैं, ताकि वे एक बड़े हिमस्खलन ऊर्जा परिमाण को बढ़ाने में सक्षम हों, जिससे एक धारणा बनती है कि MOSFET का परीक्षण विशाल हिमस्खलन ऊर्जाओं को समझने के लिए किया जाता है, और इसलिए हिमस्खलन के लिए एक अधिक स्थायित्व है।

लेकिन बड़े प्रारंभ करनेवाला का उपयोग करने की उपरोक्त विधि भ्रामक दिखती है, यही कारण है कि टेक्सास इंस्ट्रूमेंट्स इंजीनियर 0.1 mH के क्रम में छोटे अधिष्ठापन के साथ परीक्षण करते हैं, ताकि परीक्षण के तहत MOSFET उच्च हिमस्खलन वर्तमान और चरम विराम तनाव के स्तर के अधीन हो।

तो, डेटशीट में, यह हिमस्खलन ऊर्जा नहीं है, बल्कि हिमस्खलन वर्तमान है जो मात्रा में बड़ा होना चाहिए, जो बेहतर MOSFET असभ्यता प्रदर्शित करता है।

यह अंतिम परीक्षण को अत्यधिक कठोर बनाता है और जितना संभव हो उतने कमजोर MOSFETs को फ़िल्टर करने में सक्षम बनाता है।

यह परीक्षण मूल्य न केवल उत्पादन के लिए FET लेआउट पारित होने से पहले अंतिम मूल्य के रूप में उपयोग किया जाता है, बल्कि यह वह मान भी है जो डेटाशीट में दर्ज किया गया है।

अगले चरण में, उपरोक्त परीक्षण मूल्य 65% से अधिक है, ताकि अंतिम उपयोगकर्ता अपने MOSFETs के लिए सहनशीलता का एक व्यापक मार्जिन प्राप्त करने में सक्षम हो।

उदाहरण के लिए, यदि परीक्षण किया गया हिमस्खलन करंट 125 एम्प्स था, तो डेटाशीट में जो अंतिम मान दर्ज किया गया है, वह व्युत्पन्न के बाद 81 एम्प्स का होना चाहिए।

मोसेफेट हिमस्खलन वर्तमान समय बनाम हिमस्खलन में समय बिताया

एक अन्य पैरामीटर जो पावर MOSFET के साथ जुड़ा हुआ है और डेटाशीट में उल्लेख किया गया है, विशेष रूप से अनुप्रयोगों को स्विच करने के लिए डिज़ाइन किए गए MOSFET के लिए, हिमस्खलन में एवलांच करंट कैपेबिलिटी बनाम टाइम स्पेंट है। यह पैरामीटर आम तौर पर MOSFET के मामले के तापमान के संबंध में 25 डिग्री पर दिखाया जाता है। परीक्षण के दौरान केस का तापमान 125 डिग्री तक बढ़ जाता है।

इस स्थिति में MOSFET के सिलिकॉन मरने के वास्तविक जंक्शन तापमान के लिए MOSFET के मामले का तापमान बहुत करीब हो जाता है।

इस प्रक्रिया में चूंकि डिवाइस का जंक्शन तापमान बढ़ा हुआ है, आप एक निश्चित मात्रा में गिरावट देखने की उम्मीद कर सकते हैं जो काफी सामान्य है? हालाँकि, यदि परिणाम उच्च स्तर की गिरावट को दर्शाता है, तो यह स्वाभाविक रूप से कमजोर MOSFET डिवाइस के संकेतों को इंगित कर सकता है।

इसलिए डिजाइन के दृष्टिकोण से, यह सुनिश्चित करने का प्रयास किया जाता है कि 25 से 125 डिग्री के मामले में वृद्धि के लिए गिरावट 30% से अधिक न हो।

मोलसेट को हिमस्खलन करंट से कैसे बचाएं

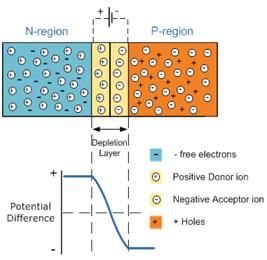

जैसा कि हमने उपरोक्त चर्चाओं से सीखा है, MOSFETs में हिमस्खलन का विकास MOSFET के बॉडी डायोड के माध्यम से उच्च वोल्टेज इंडक्टिव बैक EMF स्विचिंग के कारण होता है।

यदि यह वापस EMF वोल्टेज शरीर के डायोड की अधिकतम रेटिंग से अधिक है, तो डिवाइस में अत्यधिक गर्मी उत्पन्न करता है और बाद में नुकसान होता है।

इसका तात्पर्य यह है कि यदि आगमनात्मक ईएमएफ वोल्टेज को बाहरी रूप से रेटेड बायपास डायोड से गुजरने की अनुमति दी जाती है, तो एफईटी के नाली-एमिटर भर में हिमस्खलन की घटना को रोकने में मदद मिल सकती है।

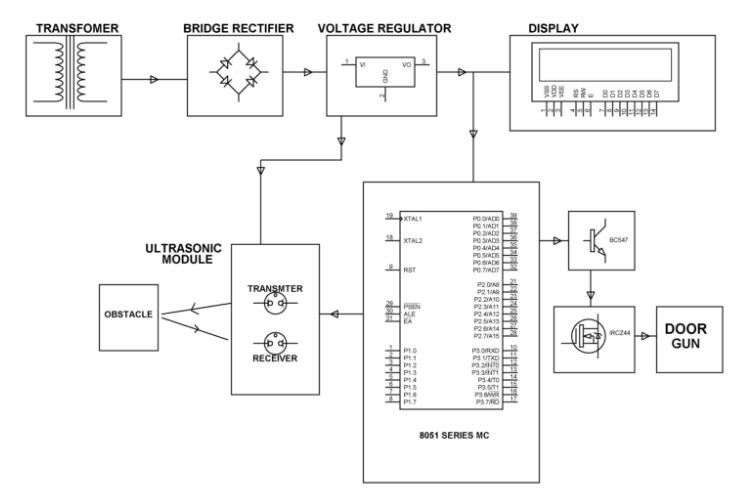

निम्नलिखित आरेख MFTFET के आंतरिक शरीर डायोड को मजबूत करने के लिए एक बाहरी नाली-एमिटर डायोड को जोड़ने के मानक डिजाइन का सुझाव देता है।

के सौजन्य से: MOSFET हिमस्खलन

की एक जोड़ी: उच्च दक्षता दहन के लिए अनुक्रमिक स्पार्क के लिए बर्बाद स्पार्क इग्निशन परिवर्तित अगला: सरल ऑनलाइन यूपीएस सर्किट