निर्देश सेट या अनुदेश सेट आर्किटेक्चर कंप्यूटर की संरचना है जो कंप्यूटर को डेटा हेरफेर के प्रसंस्करण के लिए कंप्यूटर को निर्देशित करने के लिए आदेश प्रदान करता है। निर्देश सेट में निर्देश, संबोधित करने के तरीके, मूल डेटा प्रकार, रजिस्टर, व्यवधान, अपवाद हैंडलिंग और मेमोरी आर्किटेक्चर शामिल हैं। निर्देश सेट सॉफ्टवेयर में एक दुभाषिया का उपयोग करके या प्रोसेसर के हार्डवेयर में बनाया जा सकता है। निर्देश सेट आर्किटेक्चर को सॉफ्टवेयर और हार्डवेयर के बीच एक सीमा माना जा सकता है। माइक्रोकंट्रोलर्स का वर्गीकरण और माइक्रोप्रोसेसरों को RISC और CISC इंस्ट्रक्शन सेट आर्किटेक्चर के आधार पर किया जा सकता है।

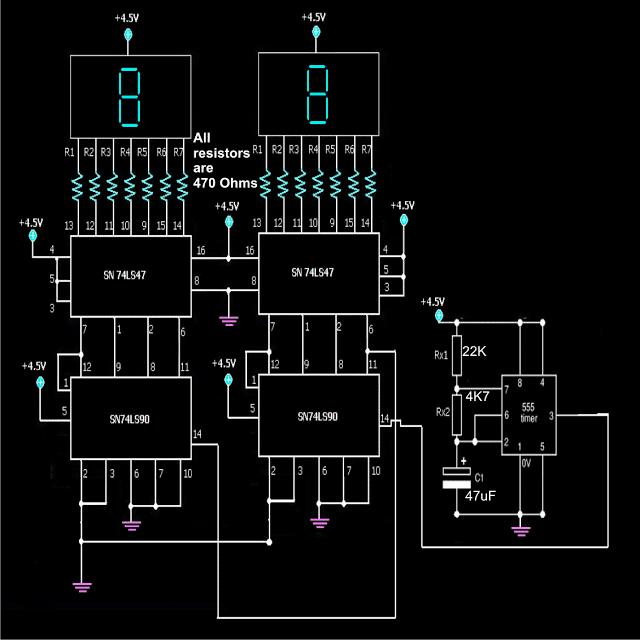

प्रोसेसर का निर्देश सेट

निर्देश सेट प्रोसेसर की कार्यक्षमता, प्रोसेसर के भंडारण तंत्र और प्रोसेसर के कार्यक्रमों को संकलित करने के तरीके सहित समर्थित है।

RISC और CISC क्या है?

RISC और CISC निम्नानुसार विस्तार किया जा सकता है:

RISC कम किए गए निर्देश सेट कंप्यूटर का प्रतिनिधित्व करता है और

CISC जटिल निर्देश सेट कंप्यूटर का प्रतिनिधित्व करता है।

आरआईएससी (कम किए गए निर्देश सेट कंप्यूटर) आर्किटेक्चर

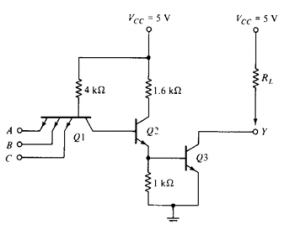

RISC आर्किटेक्चर

माइक्रोकंट्रोलर आर्किटेक्चर निर्देशों के छोटे और अत्यधिक अनुकूलित सेट का उपयोग कम किए गए निर्देश सेट कंप्यूटर या बस RISC के रूप में कहा जाता है। इसे LOAD / STORE आर्किटेक्चर भी कहा जाता है।

1970 के दशक के अंत और 1980 के दशक की शुरुआत में, RISC प्रोजेक्ट्स मुख्य रूप से स्टैनफोर्ड, यूसी-बर्कले और आईबीएम से विकसित किए गए थे। IBM शोध दल के जॉन कोक ने CISC की तुलना में तेजी से प्रसंस्करण संगणना के लिए आवश्यक निर्देशों की संख्या को कम करके RISC विकसित किया। RISC आर्किटेक्चर तेज है और CISC आर्किटेक्चर की तुलना में RISC आर्किटेक्चर के निर्माण के लिए आवश्यक चिप्स भी कम खर्चीले नहीं हैं।

आरआईएससी आर्किटेक्चर की विशिष्ट विशेषताएं

- आरआईएससी की पाइपलाइनिंग तकनीक, निर्देशों के कई हिस्सों या चरणों को एक साथ निष्पादित करती है जैसे कि सीपीयू पर प्रत्येक निर्देश को अनुकूलित किया जाता है। इसलिए, RISC प्रोसेसर में एक चक्र के निर्देश प्रति घड़ी होते हैं, और इसे वन साइकिल निष्पादन कहा जाता है।

- यह अनुकूलन करता है रजिस्टर का उपयोग RISC में रजिस्टरों की अधिक संख्या और मेमोरी के भीतर अधिक संख्या में बातचीत को रोका जा सकता है।

- सरल संबोधित मोड, यहां तक कि जटिल पते अंकगणित का उपयोग करके किया जा सकता है और / या तार्किक संचालन ।

- यह समान सामान्य उद्देश्य रजिस्टरों का उपयोग करके संकलक डिजाइन को सरल बनाता है जो किसी भी संदर्भ में किसी भी रजिस्टर का उपयोग करने की अनुमति देता है।

- पाइपलाइनिंग उपयोगों के रजिस्टरों और अनुकूलन के कुशल उपयोग के लिए, कम किए गए अनुदेश सेट की आवश्यकता होती है।

- ऑपकोड के लिए उपयोग किए जाने वाले बिट्स की संख्या कम हो जाती है।

- सामान्य तौर पर आरआईएससी में 32 या अधिक रजिस्टर होते हैं।

आरआईएससी प्रोसेसर आर्किटेक्चर के फायदे

- आरआईएससी के निर्देशों के छोटे सेट के कारण, उच्च-स्तरीय भाषा संकलक अधिक कुशल कोड का उत्पादन कर सकते हैं।

- आरआईएससी अंतरिक्ष का उपयोग करने की स्वतंत्रता की अनुमति देता है माइक्रोप्रोसेसरों इसकी सादगी के कारण।

- स्टैक का उपयोग करने के बजाय, कई आरआईएससी प्रोसेसर, तर्कों को पारित करने और स्थानीय चर रखने के लिए रजिस्टरों का उपयोग करते हैं।

- RISC फ़ंक्शन केवल कुछ मापदंडों का उपयोग करता है, और RISC प्रोसेसर कॉल निर्देशों का उपयोग नहीं कर सकते हैं, और इसलिए, एक निश्चित लंबाई निर्देशों का उपयोग करें जो पाइपलाइन के लिए आसान हैं।

- ऑपरेशन की गति को अधिकतम किया जा सकता है और निष्पादन समय को कम किया जा सकता है।

- बहुत कम निर्देश प्रारूप (चार से कम), कुछ संख्या में निर्देश (लगभग 150) और कुछ पता मोड (चार से कम) की आवश्यकता होती है।

RISC प्रोसेसर आर्किटेक्चर की कमियां

- निर्देशों की लंबाई में वृद्धि के साथ, RISC प्रोसेसर के लिए जटिलता प्रति निर्देश चक्र चरित्र के कारण निष्पादित होती है।

- RISC प्रोसेसर का प्रदर्शन ज्यादातर कंपाइलर या प्रोग्रामर पर निर्भर करता है क्योंकि CISC कोड को RISC कोड में कनवर्ट करते समय कंपाइलर का ज्ञान एक प्रमुख भूमिका निभाता है, इसलिए जेनरेट किए गए कोड की गुणवत्ता कंपाइलर पर निर्भर करती है।

- CISC कोड को RISC कोड में फेरबदल करते समय, कोड विस्तार के रूप में कहा जाता है, आकार में वृद्धि करेगा। और, इस कोड विस्तार की गुणवत्ता फिर से संकलक पर निर्भर करेगी, और मशीन के निर्देश सेट पर भी।

- RISC प्रोसेसर का पहला स्तर कैश भी RISC का एक नुकसान है, जिसमें इन प्रोसेसर में चिप पर ही बड़े मेमोरी कैश होते हैं। निर्देशों को खिलाने के लिए, उन्हें बहुत आवश्यकता होती है फास्ट मेमोरी सिस्टम ।

CISC (कॉम्प्लेक्स इंस्ट्रक्शन सेट कम्प्यूटर) आर्किटेक्चर

CISC प्रोसेसर आर्किटेक्चर का मुख्य उद्देश्य असेंबली लाइनों की कम संख्या का उपयोग करके कार्य को पूरा करना है। इस उद्देश्य के लिए, प्रोसेसर को संचालन की एक श्रृंखला निष्पादित करने के लिए बनाया गया है। जटिल निर्देश को MULT भी कहा जाता है, जो संचालित होता है मेमोरी बैंक कंप्यूटर का भंडारण और लोडिंग कार्य करने के लिए संकलक बनाने के बिना सीधे।

CISC आर्किटेक्चर

CISC आर्किटेक्चर की विशेषताएं

- कंप्यूटर वास्तुकला को सरल बनाने के लिए, CISC माइक्रोप्रोग्रामिंग का समर्थन करता है।

- CISC में पूर्वनिर्धारित निर्देशों की अधिक संख्या है जो उच्च स्तरीय भाषाओं को डिजाइन और कार्यान्वित करना आसान बनाता है।

- CISC में रजिस्टरों की संख्या कम और एड्रेसिंग मोड्स की संख्या अधिक होती है, आमतौर पर 5 से 20।

- CISC प्रोसेसर निर्देशों के निष्पादन के लिए अलग-अलग चक्र का समय लेता है - बहु-घड़ी चक्र।

- CISC के जटिल अनुदेश सेट के कारण, पाइपलाइनिंग तकनीक बहुत कठिन है।

- CISC में आमतौर पर 100 से 250 तक अधिक संख्या में निर्देश होते हैं।

- विशेष निर्देशों का उपयोग बहुत कम ही किया जाता है।

- स्मृति में परिचालनों को निर्देशों द्वारा हेरफेर किया जाता है।

CISC वास्तुकला के लाभ

- प्रत्येक मशीन भाषा निर्देश को एक माइक्रोकोड निर्देश में वर्गीकृत किया जाता है और उसी के अनुसार निष्पादित किया जाता है, और फिर मुख्य प्रोसेसर की मेमोरी में इनबिल्ट संग्रहीत किया जाता है, जिसे माइक्रोकोड कार्यान्वयन कहा जाता है।

- जैसा कि माइक्रोकोड मेमोरी मुख्य मेमोरी से तेज है, माइक्रोकोड इंस्ट्रक्शन सेट को हार्ड वायर्ड कार्यान्वयन पर काफी तेजी से कमी के बिना लागू किया जा सकता है।

- माइक्रो प्रोग्राम डिज़ाइन को संशोधित करके संपूर्ण नए इंस्ट्रक्शन सेट को संभाला जा सकता है।

- CISC, एक कार्यक्रम को लागू करने के लिए आवश्यक निर्देशों की संख्या को समृद्ध अनुदेश सेटों के निर्माण से कम किया जा सकता है और धीमी गति से मुख्य मेमोरी को कुशलतापूर्वक उपयोग करने के लिए भी बनाया जा सकता है।

- निर्देशों के सुपरसेट के कारण, जिसमें पहले के सभी निर्देश शामिल हैं, यह माइक्रो कोडिंग को आसान बनाता है।

CISC की कमियां

- अलग-अलग निर्देशों द्वारा ली गई घड़ी का समय अलग-अलग होगा - इसके कारण - मशीन का प्रदर्शन धीमा हो जाता है।

- अनुदेश सेट जटिलता और चिप हार्डवेयर बढ़ जाता है क्योंकि प्रोसेसर के हर नए संस्करण में पिछली पीढ़ियों का सबसेट होता है।

- मौजूदा निर्देशों का केवल 20% एक विशिष्ट प्रोग्रामिंग ईवेंट में उपयोग किया जाता है, भले ही अस्तित्व में कई विशेष निर्देश हैं जो अक्सर उपयोग नहीं किए जाते हैं।

- CISC निर्देशों द्वारा सशर्त कोड प्रत्येक निर्देश के साइड इफेक्ट के रूप में सेट किए जाते हैं, जो इस सेटिंग के लिए समय लेता है - और, जैसा कि बाद के निर्देश में कंडीशन कोड बिट्स को बदलता है - इसलिए, कंपाइलर को ऐसा होने से पहले कंडीशन कोड बिट्स की जांच करनी होगी।

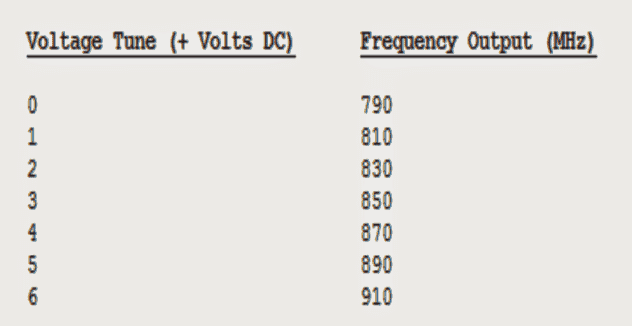

RISC बनाम। CISC

- प्रोग्रामर द्वारा RISC में अनावश्यक कोड को हटाकर बर्बाद होने वाले चक्र को रोका जा सकता है, लेकिन CISC कोड का उपयोग करते समय CISC की अक्षमता के कारण साइकिल को बर्बाद करना पड़ता है।

- RISC में, प्रत्येक निर्देश का उद्देश्य एक छोटा कार्य करना होता है जैसे कि, एक जटिल कार्य करने के लिए, एक साथ कई छोटे निर्देशों का उपयोग किया जाता है, जबकि CISC का उपयोग करके एक ही कार्य करने के लिए केवल कुछ निर्देशों की आवश्यकता होती है - क्योंकि यह जटिल कार्य करने में सक्षम होता है जैसा कि निर्देश उच्च भाषा कोड के समान हैं।

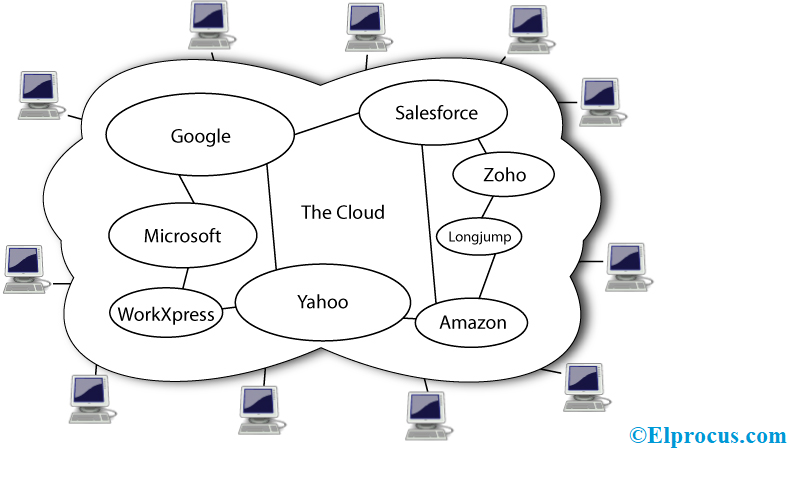

- CISC का उपयोग आमतौर पर कंप्यूटर के लिए किया जाता है जबकि RISC का उपयोग स्मार्ट फोन, टैबलेट और अन्य इलेक्ट्रॉनिक उपकरणों के लिए किया जाता है।

निम्नलिखित आंकड़ा RISC और CISC के बीच अधिक अंतर दिखाता है

RISC बनाम। CISC

इस प्रकार, यह लेख RISC और CISC आर्किटेक्चर के RISC और CISC प्रोसेसर्स आर्किटेक्चर के फायदे और RISC और CISC की कमियां और RISC और CISC आर्किटेक्चर के बीच के अंतर के बारे में चर्चा करता है। RISC और CISC आर्किटेक्चर के बारे में अधिक जानकारी के लिए, कृपया नीचे टिप्पणी करके अपने प्रश्नों को पोस्ट करें।

फ़ोटो क्रेडिट:

- द्वारा प्रोसेसर का निर्देश सेट Arstechnica

- द्वारा RISC आर्किटेक्चर lsi- प्रतियोगिता

- RISC बनाम CISC द्वारा शस्त्रीकरण