हमारे दिन-प्रतिदिन के जीवन में, हम कई प्रकारों का उपयोग करते हुए अक्सर दूसरों के साथ संवाद करते हैं संचार प्रणाली । इस संचार प्रणाली को विभिन्न प्रकारों में वर्गीकृत किया जा सकता है, जैसे कि रेडियो संचार प्रणाली, दूरसंचार प्रणाली, वायरलेस संचार प्रणाली , ऑप्टिकल संचार प्रणाली, और इतने पर। इन सभी संचार प्रणालियों को कुशलतापूर्वक संचालित करने के लिए, हमें कुछ नियंत्रण प्रणालियों की आवश्यकता होती है, जैसे कि एक फेज़-लॉक लूप, सहकारी नियंत्रण, नेटवर्क नियंत्रण और इतने पर।

चरण-बंद लूप (PLL) क्या है?

चरण-बंद लूप का उपयोग कई संचार प्रणालियों, कंप्यूटरों और कई में विभिन्न कार्यों को नियंत्रित करने के लिए एक नियंत्रण प्रणाली के रूप में किया जाता है इलेक्ट्रॉनिक अनुप्रयोगों । इसका उपयोग आउटपुट सिग्नल उत्पन्न करने के लिए किया जाता है जिसमें इनपुट सिग्नल चरण से संबंधित चरण होता है।

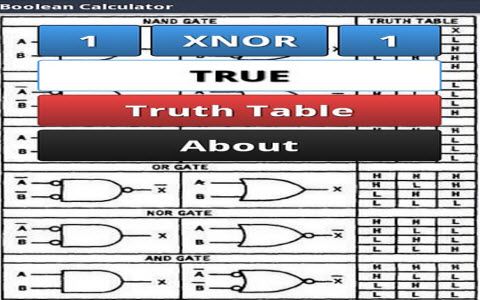

विभिन्न प्रकार के PLL होते हैं जैसे एनालॉग या रैखिक PLL, डिजिटल PLL, सॉफ्टवेयर PLL, Neuronal PLL और सभी डिजिटल PLL।

चरण बंद लूप ऑपरेशन

संचार प्रणालियों में, पीएलएल ऑपरेशन को विचार करके समझाया जा सकता है एनालॉग और डिजिटल सिस्टम ।

संचार प्रणालियों में एनालॉग चरण-बंद लूप

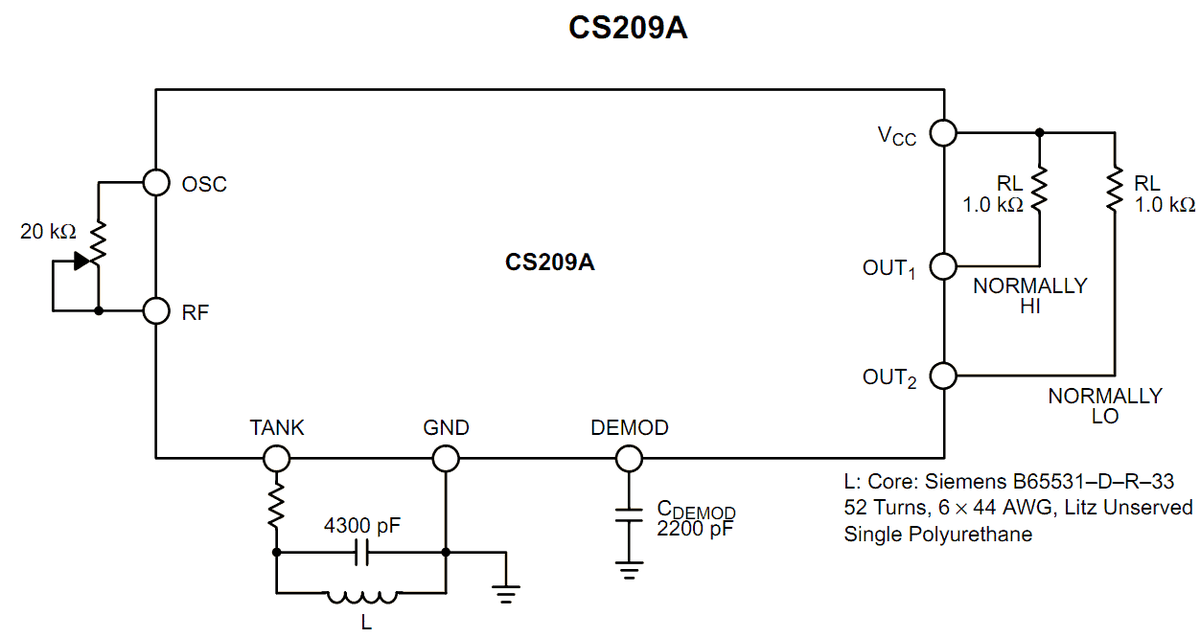

मूल रूप से PLL सर्वो लूप का एक रूप है और एक मूल PLL में तीन प्रमुख तत्व होते हैं, अर्थात् चरण तुलनित्र / डिटेक्टर, लूप फ़िल्टर और वोल्टेज नियंत्रित थरथरानवाला ।

चरण बंद लूप

PPL ऑपरेशन के पीछे की प्रमुख अवधारणा दो संकेतों (आमतौर पर इनपुट और आउटपुट सिग्नल चरणों की तुलना की जाती है) के चरणों की तुलना है। इस प्रकार, इनपुट और आउटपुट सिग्नल के बीच चरण अंतर का उपयोग लूप आवृत्ति को नियंत्रित करने के लिए किया जा सकता है। भले ही गणितीय विश्लेषण बहुत जटिल है, लेकिन पीएलएल का संचालन बहुत सरल है।

कई संचार प्रणालियों में, PLL का उपयोग विभिन्न उद्देश्यों के लिए किया जाता है:

- चरण का पालन करने के लिए या आवृति का उतार - चढ़ाव , इसका उपयोग डेमोडुलेटर के रूप में किया जाता है।

- अलग-अलग आवृत्तियों के साथ दो संकेतों को ट्रैक या सिंक्रनाइज़ करने के लिए।

- छोटे संकेतों से बड़े शोर को हटाने के लिए।

नीचे दिया गया आंकड़ा मूल PLL को दर्शाता है जिसमें फेज़ डिटेक्टर, वोल्टेज नियंत्रित ऑस्किलेटर (VCO), लूप फ़िल्टर शामिल हैं।

PLL का वोल्टेज नियंत्रित थरथरानवाला एक संकेत पैदा करता है और VCO से यह संकेत चरण डिटेक्टर को दिया जाता है। चरण डिटेक्टर इस संकेत की संदर्भ संकेत के साथ तुलना करता है और इस प्रकार, एक त्रुटि वोल्टेज या अंतर वोल्टेज पैदा करता है। चरण डिटेक्टर का यह त्रुटि संकेत किसी भी सिग्नल -if के उच्च आवृत्ति तत्वों को हटाने के लिए कम-पास फिल्टर को खिलाया जाता है, और लूप के कई गुणों को नियंत्रित करने के लिए। फिर, लूप फिल्टर का आउटपुट वोल्टेज नियंत्रित थरथरानर के नियंत्रण टर्मिनल के लिए ट्यूनिंग वोल्टेज की आपूर्ति करने के लिए खिलाया जाता है।

इस ट्यूनिंग वोल्टेज में परिवर्तन को दो संकेतों (इनपुट और आउटपुट) और इस प्रकार, उनके बीच की आवृत्ति के बीच चरण अंतर को कम करने के लिए महसूस किया जाता है। प्रारंभ में PLL लॉक नहीं होता है और त्रुटि वोल्टेज संदर्भ की ओर VCO आवृत्ति को बढ़ाती है जब तक कि त्रुटि को और कम नहीं किया जा सकता है और फिर लूप लॉक हो जाता है।

दो संकेतों (इनपुट और आउटपुट) के बीच वास्तविक त्रुटि बहुत छोटे स्तर तक कम हो जाती है एक एम्पलीफायर का उपयोग करना वोल्टेज नियंत्रित थरथरानवाला और एक चरण डिटेक्टर के बीच में। यदि पीएलएल बंद है, तो एक स्थिर-राज्य त्रुटि वोल्टेज का उत्पादन किया जाएगा। यह स्थिर-राज्य त्रुटि वोल्टेज दर्शाता है कि संदर्भ संकेत और VCO के बीच कोई चरण अंतर परिवर्तन नहीं है। इस प्रकार, हम कह सकते हैं कि दो संकेतों (इनपुट और आउटपुट सिग्नल) की आवृत्ति बिल्कुल समान है।

संचार प्रणालियों में डिजिटल चरण बंद लूप

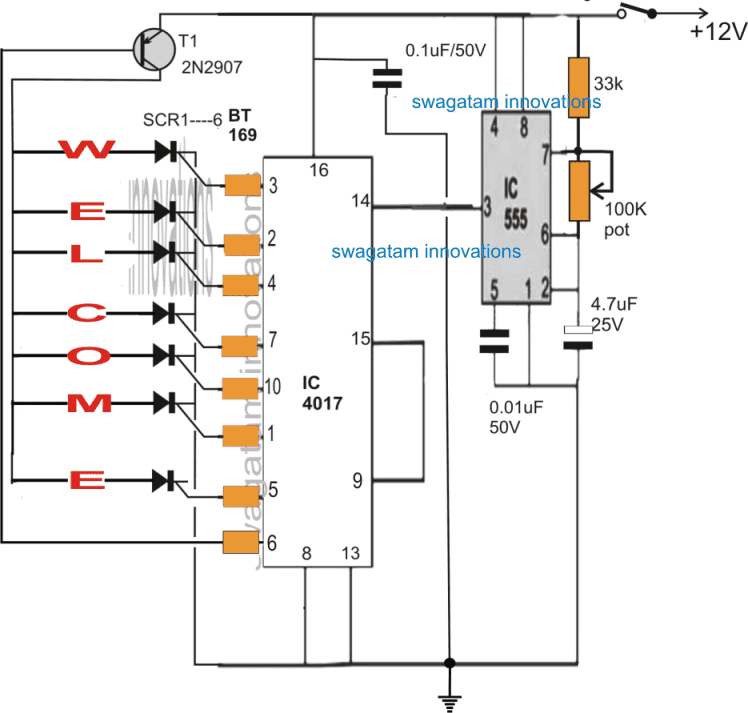

सामान्य एनालॉग PLL में एक एनालॉग-चरण डिटेक्टर, वोल्टेज नियंत्रित थरथरानवाला और कम-पास फिल्टर होते हैं। इसी तरह, डिजिटल-फेज़ लॉक लूप में डिजिटल-फ़ेज़ डिटेक्टर होते हैं, a सीरियल-शिफ्ट रजिस्टर , एक स्थिर स्थानीय घड़ी संकेत।

डिजिटल फेज लॉक्ड

डिजिटल इनपुट नमूनों को प्राप्त सिग्नल से निकाला जाता है और ये नमूने सीरियल शिफ्ट रजिस्टर द्वारा प्राप्त किए जाते हैं, जो स्थानीय-घड़ी सिग्नल से आपूर्ति की गई घड़ी दालों द्वारा संचालित होता है। एक चरण-सुधारक सर्किट जो स्थानीय घड़ी लेता है, का उपयोग चरण में एक स्थिर-घड़ी संकेत को पुन: प्राप्त करने के लिए किया जाता है, प्राप्त संकेत चरण से मेल खाने के लिए धीमी चरण समायोजन द्वारा प्राप्त संकेत के साथ।

यह समायोजन सुधार तर्क का उपयोग करके प्रत्येक बिट के एक उच्च गति के नमूने के आधार पर किया जा सकता है। स्थानीय घड़ी की गति पर प्राप्त सिग्नल के नमूने द्वारा प्राप्त सिग्नल सिग्नल को शिफ्ट रजिस्टर में रखा गया है।

प्राप्त संकेत के नमूनों के सेट को देखकर आवश्यक चरण समायोजन का पता लगाया जा सकता है। दो घड़ियों को चरण में कहा जाता है यदि और केवल तभी प्राप्त बिट केंद्र शिफ्ट रजिस्टर के केंद्र में होता है। चरण समायोजक क्षतिपूर्ति करने के लिए अभिप्रेत है यदि पुनर्जीवित घड़ी लैग या संदर्भ सिग्नल का नेतृत्व करती है।

चरण बंद लूप के आवेदन

- PLL का उपयोग अक्सर सिंक्रोनाइज़ेशन के लिए किया जाता है और अंतरिक्ष संचार में बिट सिंक्रोनाइज़ेशन, प्रतीक सिंक्रोनाइज़ेशन, सुसंगत डिमॉड्यूलेशन और थ्रेशोल्ड एक्सटेंशन के लिए उपयोग किया जाता है।

- पीएलएल का उपयोग करके आवृत्ति संग्राहक संकेतों को ध्वस्त किया जा सकता है।

- नई आवृत्ति जो संदर्भ आवृत्ति की एक बहु है रेडियो संचार ट्रांसमीटर , और नई आवृत्ति के साथ संदर्भ आवृत्ति की स्थिरता बनाए रखने के द्वारा संश्लेषित PLLs द्वारा प्राप्त किया जा सकता है।

- कई संचार प्रणालियों, कंप्यूटरों और कई में PLL के लिए कई अनुप्रयोग हैं विद्युत सर्किट ।

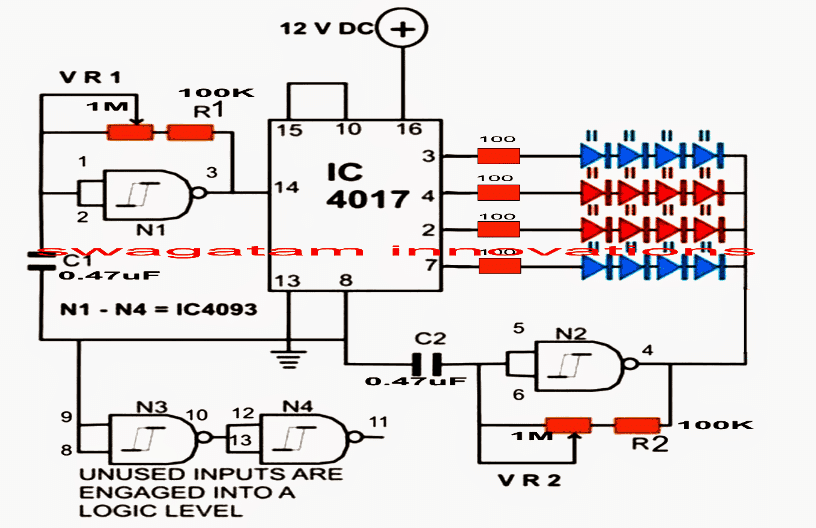

- पीएलएल के नीचे दिए गए आवेदन में वोल्टेज के रूप में पीएलएल के उपयोग का वर्णन है आवृत्ति कनवर्टर ।

पीएलएल का उपयोग करते हुए वोल्टेज से आवृत्ति कनवर्टर (वीएफसी)

संचार प्रणालियों में, पूरी सटीकता के साथ लंबी दूरी तक सिग्नल भेजने (यहां एनालॉग सिग्नल पर विचार करने) की आवश्यकता होती है। इस प्रयोजन के लिए, एक वोल्टेज-टू-आवृत्ति कनवर्टर का उपयोग किया जाता है, क्योंकि ऑप्टिकल आइसोलेटर, समाक्षीय या मुड़-जोड़ी लाइनों, रेडियो लिंक, का उपयोग करके लंबी दूरी पर कोई हस्तक्षेप किए बिना आवृत्ति संकेत भेजना आसान है। ऑप्टिकल फाइबर लिंक ।

दो प्रकार के वोल्टेज-टू-फ़्रीक्वेंसी कन्वर्टर्स हैं मल्टीवीब्रेटर प्रकार VFC और चार्ज बैलेंस प्रकार VFC।

मल्टीवीब्रेटर टाइप VFC

मल्टीवीब्रेटर VFC

मल्टीवीब्रेटर प्रकार वीएफसी में, संधारित्र को चार्ज किया जाता है और इनपुट वोल्टेज से प्राप्त वर्तमान का उपयोग करके छुट्टी दे दी जाती है। स्विचिंग थ्रेसहोल्ड सेट करने के लिए स्थिर संदर्भ इनपुट दिया जाता है, और आउटपुट आवृत्ति इनपुट वोल्टेज के लिए आनुपातिक होती है और एकता चिह्न-स्थान अनुपात होती है।

चार्ज बैलेंस टाइप VFC

शेष राशि VFC

चार्ज बैलेंस VFC में एक इंटीग्रेटर, एक तुलनित्र और एक सटीक चार्ज सोर्स होते हैं। जब भी इंटीग्रेटर को कोई इनपुट दिया जाता है, वह चार्ज हो जाता है और यदि इस इंटीग्रेटर का आउटपुट तुलनित्र सीमा तक पहुँच जाता है, तो चार्ज सोर्स ट्रिगर और फिक्स्ड चार्ज हो जाता है। इंटीग्रेटर से हटा दिया जाता है। चार्ज हटाए गए दर को चार्ज की गई आपूर्ति दर के बराबर होना चाहिए, चार्ज सोर्स ट्रिगर आवृत्ति और इंटीग्रेटर के इनपुट एक दूसरे के लिए आनुपातिक होगा।

इस प्रकार, इस लेख के बारे में एक संक्षिप्त विवरण देता है चरण बंद लूप प्रणाली संचार प्रणाली में। इसके अलावा, इस लेख को तकनीकी रूप से आपके सुझावों और प्रश्नों के आधार पर बढ़ाया जा सकता है। इसलिए, आप अपनी टिप्पणी नीचे पोस्ट करके किसी भी तकनीकी सहायता के लिए हमसे संपर्क कर सकते हैं।