FET के दो मुख्य प्रकार जो वर्तमान में मौजूद हैं: JFETs और MOSFETs।

MOSFETs को और अधिक विघटन प्रकार में वर्गीकृत किया जा सकता है और वृद्धि प्रकार। ये दोनों प्रकार MOSFETs के संचालन के मूल मोड को परिभाषित करते हैं, जबकि MOSFET शब्द स्वयं धातु-ऑक्साइड-सेमीकंडक्टर-फील्ड-प्रभाव ट्रांजिस्टर का संक्षिप्त नाम है।

इस तथ्य के कारण कि दो प्रकार की अलग-अलग कार्य विशेषताएं हैं, हम उनमें से प्रत्येक का मूल्यांकन अलग-अलग लेखों में करेंगे।

एन्हांसमेंट और डिप्लेशन MOSFET के बीच अंतर

मूल रूप से, वृद्धि MOSFETs के विपरीत, कमी MOSFETs गेट-टू-सोर्स टर्मिनलों (VGS) के पार 0 V की उपस्थिति में भी एक राज्य में हैं।

एक वृद्धि MOSFET के लिए, गेट-टू-सोर्स वोल्टेज (VGS) इसके गेट-टू-सोर्स थ्रेसहोल्ड वोल्टेज (VGS (th)) से ऊपर होना चाहिए आचरण करने के लिए ।

हालांकि, एक एन-चैनल की कमी MOSFET के लिए, इसका VGS (th) मान 0 V से ऊपर है। इसका मतलब है कि भले ही VGS = 0 V, एक कमी MOSFET वर्तमान का संचालन करने में सक्षम है। इसे बंद करने के लिए, एक कमी MOSFET के VGS को VGS (th) (नकारात्मक) से कम करने की आवश्यकता है।

इस वर्तमान लेख में हम कमी प्रकार MOSFET पर चर्चा करेंगे, जिसके बारे में कहा जाता है कि इसमें JFET के मिलान की विशेषताएँ होती हैं। समानता आई के पास कट-ऑफ और संतृप्ति के बीच हैDSS

मूल निर्माण

Fig.5.23 एक n- चैनल की कमी की मूल आंतरिक संरचना को दर्शाता है MOSFET- प्रकार।

हम सिलिकॉन बेस का उपयोग करके बनाई गई पी-प्रकार की सामग्री का एक ब्लॉक पा सकते हैं। इस ब्लॉक को सब्सट्रेट कहा जाता है।

सब्सट्रेट आधार या नींव है जिस पर MOSFET का निर्माण किया जाता है। कुछ MOSFETs के लिए इसे आंतरिक रूप से 'स्रोत' टर्मिनल के साथ जोड़ा जाता है। इसके अलावा, कई उपकरण SS के रूप में एक अतिरिक्त आउटपुट प्रदान करते हैं, जिसमें 4-टर्मिनल MOSFET की विशेषता होती है, जैसा कि Fig.5.23 में बताया गया है

नाली और स्रोत टर्मिनलों को एन-डोप किए गए स्थानों के लिए प्रवाहकीय संपर्कों के माध्यम से जोड़ा जाता है, और एन-चैनल के माध्यम से संलग्न किया जाता है, जैसा कि एक ही आंकड़े में संकेत दिया गया है।

गेट एक धातु की परत से भी जुड़ा हुआ है, हालांकि यह एन-चैनल से सिलिकॉन डाइऑक्साइड की एक पतली परत के माध्यम से अछूता है (SiO)दो) है।

सी.आई.ओ.दोइन्सुलेशन गुण का एक अनूठा रूप रखता है जिसे ढांकता हुआ कहा जाता है जो बाहरी रूप से लगाए गए विद्युत क्षेत्र की प्रतिक्रिया में अपने भीतर एक विरोधी विद्युत क्षेत्र बनाता है।

एक इन्सुलेट परत होने के नाते, सामग्री SiOदोहमें निम्नलिखित महत्वपूर्ण जानकारी प्रदान करता है:

इस सामग्री के साथ गेट टर्मिनल और मस्जिद चैनल के बीच एक पूर्ण अलगाव विकसित किया गया है।

इसके अलावा, यह SiO के कारण हैदोमस्जिद का द्वार बेहद उच्च स्तर के इनपुट प्रतिबाधा की सुविधा देने में सक्षम है।

इस महत्वपूर्ण उच्च इनपुट प्रतिबाधा संपत्ति के कारण, गेट वर्तमान Iजीवस्तुतः किसी भी dc- पक्षपाती MOSFET कॉन्फ़िगरेशन के लिए शून्य amps है।

मूल संचालन और विशेषताएँ

जैसा कि Fig.5.24 में देखा जा सकता है, दो वोल्टेज को एक साथ जोड़कर शून्य वोल्टेज पर स्रोत वोल्टेज के गेट को कॉन्फ़िगर किया गया है, जबकि एक वोल्टेज वी।डी एसनाली और स्रोत टर्मिनलों पर लागू किया जाता है।

उपरोक्त सेटिंग के साथ, ड्रेन साइड एन-चैनल मुक्त इलेक्ट्रॉनों द्वारा एक सकारात्मक क्षमता स्थापित करता है, साथ ही जेएफएफ चैनल के माध्यम से एक समतुल्य वर्तमान। इसके अलावा, परिणामी वर्तमान वीजी एस= 0V अभी भी I के रूप में पहचाना जा रहा हैडीएसएस, जैसा कि अंजीर में दिया गया है

हम देख सकते हैं कि Fig.5.26 में गेट स्रोत वोल्टेज वीजी एस-1 वी के रूप में एक नकारात्मक क्षमता दी जाती है।

यह नकारात्मक क्षमता इलेक्ट्रॉनों को पी-चैनल सब्सट्रेट (चार्ज रेपेल के बाद से) की ओर ले जाने की कोशिश करती है, और पी-चैनल सब्सट्रेट से छेद खींचती है (क्योंकि विपरीत चार्ज आकर्षित होते हैं)।

इस नकारात्मक पूर्वाग्रह वी पर कितना बड़ा हैजी एसछिद्रों और इलेक्ट्रॉनों का एक पुनर्संयोजन होता है, जिसके परिणामस्वरूप चालन के लिए उपलब्ध एन-चैनल में मुक्त इलेक्ट्रॉनों की कमी होती है। नकारात्मक पूर्वाग्रह के उच्च स्तर के परिणामस्वरूप पुनर्संयोजन की उच्च दर होती है।

उपरोक्त नकारात्मक पूर्वाग्रह की स्थिति में वृद्धि के परिणामस्वरूप, नाली की धारा कम हो जाती है, जो V के लिए Fig.5.25 में सिद्ध होती हैजी एसवी के स्तरजी एस= -1, -2 और इसके बाद, जब तक -6 वी का पिंच-ऑफ मार्क नहीं।

एक परिणाम के रूप में स्थानांतरण वक्र भूखंड के साथ-साथ नाली वर्तमान एक की तरह आगे बढ़ता है जेएफईटी।

अब, सकारात्मक वी के लिएजी एसमान, गेट पॉजिटिव लीवरेज करंट के कारण पी-टाइप सब्सट्रेट से अतिरिक्त इलेक्ट्रॉनों (फ्री कैरियर्स) को आकर्षित करेगा। यह त्वरक कणों में परिणामी टक्करों के रास्ते से नए वाहक स्थापित करेगा।

जैसा कि गेट-टू-सोर्स वोल्टेज सकारात्मक दर से ऊपर जाता है, ड्रेन करंट तेजी से वृद्धि को दर्शाता है, जैसा कि ऊपर चर्चा की गई समान कारणों के लिए Fig.5.25 में साबित हुआ है।

V के घटता के बीच का अंतर विकसित हुआजी एस= 0 वी और वीजी एस= +1 विशिष्ट रूप से वह राशि दिखाता है जिसके द्वारा V की 1 - V भिन्नता के कारण वर्तमान में वृद्धि हुई हैजी एस

ड्रेन करंट के तेजी से बढ़ने के कारण हमें अधिकतम करंट रेटिंग के बारे में सावधान रहना चाहिए, अन्यथा यह पॉजिटिव गेट वोल्टेज की सीमा को पार कर सकता है।

उदाहरण के लिए, उपकरण में टाइप के लिए चित्र 5 में दिखाया गया हैजी एस= + 4V के कारण नाली का प्रवाह 22.2 mA पर बढ़ जाएगा, जो डिवाइस की अधिकतम ब्रेकडाउन सीमा (वर्तमान) को पार कर सकता है।

उपरोक्त स्थिति से पता चलता है कि सकारात्मक गेट-टू-सोर्स वोल्टेज का उपयोग चैनल में मुफ्त वाहक की मात्रा पर एक बढ़ाया प्रभाव उत्पन्न करता है, जब वी के विपरीत।जी एस= 0 वी।

यही कारण है कि नाली या स्थानांतरण विशेषताओं पर सकारात्मक गेट वोल्टेज क्षेत्र आमतौर पर के रूप में जाना जाता है वृद्धि क्षेत्र । यह क्षेत्र कट-ऑफ और I के संतृप्ति स्तर के बीच स्थित हैडीएसएसया कमी क्षेत्र।

एक उदाहरण समस्या का समाधान

लाभ और अनुप्रयोग

एन्हांसमेंट-मोड MOSFETs के विपरीत, जहां हम शून्य गेट-टू-सोर्स वोल्टेज के जवाब में ड्रेन करंट को शून्य पर गिराते हुए पाते हैं, आधुनिक डेप्लेक्शन-मोड FET में जीरो गेट वोल्टेज के साथ ध्यान देने योग्य करंट की सुविधा है। सटीक होने के लिए, ड्रेन-टू-सोर्स प्रतिरोध शून्य वोल्टेज में आमतौर पर 100 ओम होता है।

जैसा कि ऊपर दिए गए ग्राफ़ में संकेत दिया गया है, ओएन-प्रतिरोध आरडीएस(पर)बनाम एनालॉग सिग्नल रेंज एक व्यावहारिक रूप से फ्लैट प्रतिक्रिया की तरह दिखती है। यह विशेषता, इन उन्नत घटाव प्रकार के डिवाइस के कम समाई स्तर के साथ संयोजन के रूप में, उन्हें ऑडियो और वीडियो स्विचिंग अनुप्रयोगों के लिए एनालॉग स्विच के रूप में विशेष रूप से आदर्श होने की अनुमति देता है।

कमी मोड- MOSFET की 'सामान्य रूप से ऑन' विशेषता डिवाइस को FET के मौजूदा नियामकों के लिए पूरी तरह से उपयुक्त बनाती है।

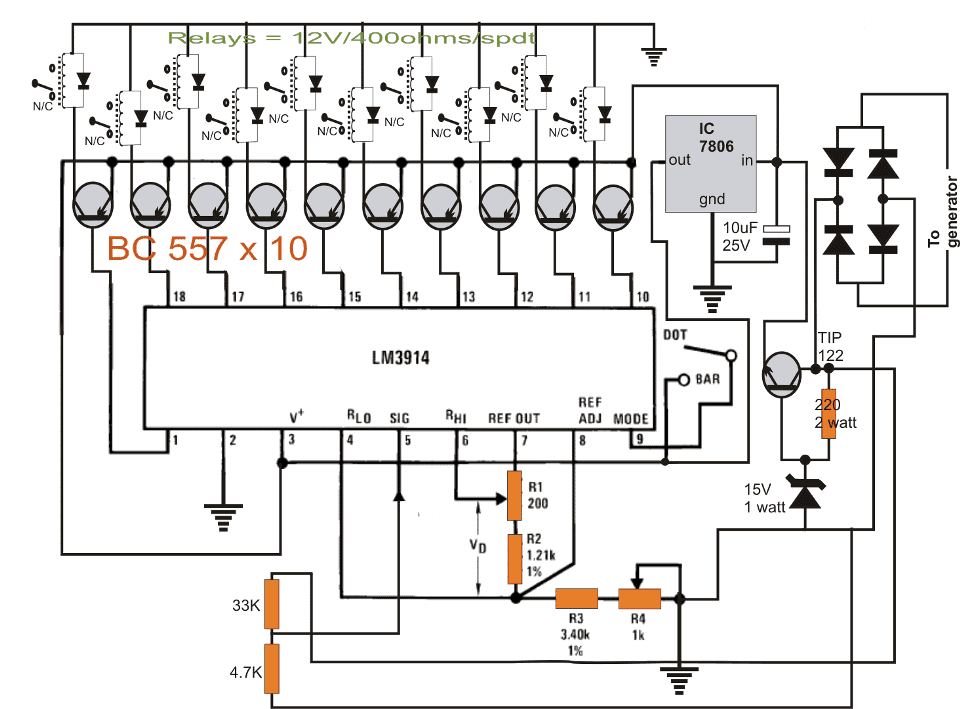

इस तरह के एक उदाहरण सर्किट को निम्न आकृति में देखा जा सकता है।

सूत्र का उपयोग करके रुपये का मूल्य निर्धारित किया जा सकता है:

आररों= वीजीएसबंद[१ - (मैंघ/मैंडीएसएस)१/२] / मैंघ

कहां है मैंघ आउटपुट पर आवश्यक रेगुलेटेड करंट की मात्रा है।

वर्तमान-स्रोत एप्लिकेशन में कमी-मोड MOSFETs का मुख्य लाभ उनकी न्यूनतम नाली समाई है, जो उन्हें कम-इनपुट रिसाव, मध्यम-गति (> 50 V / us) सर्किटों में पूर्वाग्रह अनुप्रयोगों के लिए उपयुक्त बनाता है।

नीचे दिया गया आंकड़ा एक डबल-लीकेज फ़ंक्शन FET का उपयोग करके कम-इनपुट-लीकेज करंट डिफरेंशियल फ्रंट-एंड को प्रदर्शित करता है।

सामान्यतया, JFET के दोनों ओर ID = 500 uA पर पक्षपाती होने जा रहा है। इसलिए, मुआवजा और आवारा समाई चार्ज करने के लिए वर्तमान प्राप्य 2आईडी या, 1.0 एमए जैसे मामलों में प्रतिबंधित हो जाता है। जेएफईटी की संगत विशेषताएं उत्पादन-सिद्ध हैं और डेटशीट पर आश्वस्त हैं।

Cs इनपुट स्टेज 'टेल' करंट सोर्स के आउटपुट कैपेसिटेंस का प्रतीक है। गैर-इनवर्टिंग एम्पलीफायरों में यह समाई महत्वपूर्ण है, इस तथ्य के कारण कि इनपुट चरण इस नेटवर्क में महत्वपूर्ण सिग्नल एक्सचेंज का अनुभव करता है, और सीएसएस में चार्जिंग धाराएं बड़ी हो सकती हैं। यदि सामान्य वर्तमान स्रोतों को नियोजित किया जाता है, तो यह पूंछ समाई गैर-इनवर्टिंग सर्किट में ध्यान देने योग्य स्लीव-रेट में गिरावट के लिए जिम्मेदार हो सकती है (इनवर्टरिंग अनुप्रयोगों की तुलना में, जहां Cs में चार्जिंग धाराएं न्यूनतम होती हैं)।

के रूप में देखा जा सकता है दर में गिरावट:

1 / 1+ (Cs / Sc)

जब तक Cs Cc (क्षतिपूर्ति संधारित्र) से कम है, तब तक शायद ही कभी दर में कोई भिन्नता हो सकती है। DMOS FET, Cs के साथ काम करना लगभग 2 pF हो सकता है। यह रणनीति स्लीव-रेट में भारी सुधार पैदा करती है। जहाँ वर्तमान में 1 से 5 mA से अधिक के घाटे की आवश्यकता होती है, वहां डिवाइस को एन्हांसमेंट मोड में पक्षपाती बनाया जा सकता है, ताकि अधिकतम उत्पादन V2 +2.5 V के लिए 20 mA के रूप में उत्पन्न हो, जिसमें न्यूनतम आउटपुट कैपेसिटेंस एक प्रमुख पहलू होता है।

नीचे दिया गया अगला एप्लिकेशन एक उचित एन्हांसमेंट-मोड करंट सोर्स सर्किट प्रदर्शित करता है।

एक 'सामान्य रूप से -on' एनालॉग स्विच उन आवश्यकताओं के लिए बनाया जा सकता है जहां आपूर्ति वोल्टेज की विफलता के दौरान मानक स्थिति आवश्यक हो जाती है, उदाहरण के लिए परीक्षण उपकरण के स्वचालित रेंज में या स्विच ऑन पर तर्क सर्किट के सटीक स्टार्ट-अप सुनिश्चित करने के लिए।

डिवाइस की कम नकारात्मक दहलीज वोल्टेज बुनियादी ड्राइव पूर्वापेक्षाएं प्रदान करती है और न्यूनतम वोल्टेज के साथ काम करने की अनुमति देती है।

नीचे दिए गए सर्किट में किसी भी कमी-मोड DMOS एनालॉग स्विच के लिए सामान्य पूर्वाग्रह कारक प्रदर्शित होते हैं।

डिवाइस को स्विच ऑफ करने के लिए, गेट पर एक नकारात्मक वोल्टेज आवश्यक हो जाता है। यह कहते हुए कि, जब FET को सकारात्मक गेट वोल्टेज का उपयोग करके अतिरिक्त रूप से बढ़ाया जाता है, तो इसे ऑन-रेजिस्टेंस को कम किया जा सकता है, जो इसे विशेष रूप से एन्हांसमेंट-मोड क्षेत्र के साथ-साथ रिक्तीकरण मोड में सक्षम करता है।

इस प्रतिक्रिया को निम्नलिखित ग्राफ में देखा जा सकता है।

यूनिट के उच्च आवृत्ति लाभ, इसके कम समाई मूल्यों के साथ मिलकर, 'बढ़ी हुई योग्यता का आंकड़ा' प्रदान करता है। यह वास्तव में वीएचएफ और यूएचएफ प्रवर्धन में एक महत्वपूर्ण तत्व है, जो एफईटी के लाभ-बैंडविड्थ उत्पाद (जीबीडब्ल्यू) को निर्दिष्ट करता है, जिसे निम्नानुसार दर्शाया जा सकता है:

GBW = gfs / 2 अनुकरणीय (सीमें+ सीबाहर)

पी-चैनल डिप्लेशन-प्रकार MOSFET

पी-चैनल घटाव-प्रकार MOSFET का निर्माण अंजीर में दिखाया गया है, जो.5.5.23 में दिखाया गया है। मतलब, सब्सट्रेट अब n-type का रूप ले लेता है और चैनल P-टाइप बन जाता है, जैसा कि नीचे Fig.5.28a में देखा जा सकता है।

टर्मिनल पहचान अपरिवर्तित बनी हुई है, लेकिन वोल्टेज और वर्तमान ध्रुवीयताएं उलट जाती हैं, जैसा कि एक ही आंकड़े में संकेत दिया गया है। डब्लू 5 को छोड़कर, ड्रेन की विशेषताओं को चित्र 5 में दिखाया गया हैडी एससाइन इन करें जो इस मामले में एक नकारात्मक मूल्य प्राप्त करेगा।

नाली वर्तमान मैंघइस मामले में एक सकारात्मक ध्रुवता भी दिखाता है, ऐसा इसलिए है क्योंकि हम पहले ही इसकी दिशा को उलट चुके हैं। वीजी एसविपरीत ध्रुवीयता को दर्शाता है, जो समझ में आता है, जैसा कि अंजीर में दिखाया गया है।

क्योंकि वीजी एसजैसा कि अंजीर में विशेषताओं के लिए दर्पण छवि का उत्पादन किया जाता है, जैसा कि Fig.5,28b में दिखाया गया है।

मतलब, पॉजिटिव V में ड्रेन करंट बढ़ता हैजी एसV पर कट-ऑफ पॉइंट से क्षेत्रजी एस= वीपी जब तक मैंडीएसएस, तब यह V के ऋणात्मक मान के रूप में बढ़ता रहता हैजी एसउदय होना।

प्रतीक

एक n- और पी-चैनल कमी-प्रकार MOSFET के लिए चित्रमय संकेत उपरोक्त अंजीर में देखे जा सकते हैं। 5.29।

डिवाइस की सही संरचना का प्रतिनिधित्व करने के लिए चयनित प्रतीकों का उद्देश्य जिस तरह से देखें।

गेट और चैनल के बीच एक सीधा इंटरकनेक्शन (गेट इंसुलेशन के कारण) की अनुपस्थिति को गेट और सिंबल के अलग-अलग टर्मिनलों के बीच के अंतर से दर्शाया जाता है।

ऊर्ध्वाधर रेखा जो चैनल का प्रतिनिधित्व करती है नाली और स्रोत के बीच जुड़ी हुई है और सब्सट्रेट द्वारा 'आयोजित' की जाती है।

इस तथ्य को उजागर करने के लिए प्रत्येक प्रकार के चैनल के लिए प्रतीकों के दो समूहों को ऊपर दिए गए आंकड़े में सुसज्जित किया गया है कि कुछ उपकरणों में सब्सट्रेट बाहरी रूप से सुलभ हो सकता है जबकि अन्य में यह नहीं देखा जा सकता है।

MOSFET (वृद्धि-प्रकार)

हालांकि कमी प्रकार और वृद्धि प्रकार MOSFETs उनकी आंतरिक संरचनाओं और कार्यात्मक मोड के साथ समान दिखते हैं, उनकी विशेषताएं काफी भिन्न हो सकती हैं।

ड्रेन करंट का मुख्य अंतर जो कट-ऑफ एक्शन के लिए गेट-टू-सोर्स वोल्टेज के एक विशिष्ट स्तर पर निर्भर करता है।

संक्षेप में, एक एन-चैनल एन्हांसमेंट-प्रकार MOSFET एक सकारात्मक गेट / स्रोत वोल्टेज के साथ काम कर सकता है, इसके बजाय नकारात्मक क्षमता की एक सीमा होती है जो सामान्य रूप से एक कमी प्रकार MOSFET को प्रभावित कर सकती है।

मूल निर्माण

आप निम्नलिखित में एन-चैनल एन्हांसमेंट-प्रकार MOSFET की कल्पना कर सकते हैं

अंजीर। 5.31।

एक पी-प्रकार सामग्री अनुभाग एक सिलिकॉन बेस के माध्यम से बनाया जाता है, और जैसा कि सब्सट्रेट के रूप में कहा जाता है, उससे पहले सीखा।

कुछ अवसरों पर यह सब्सट्रेट आंतरिक रूप से स्रोत पिन के साथ घट-प्रकार MOSFET में संलग्न होता है, जबकि कुछ उदाहरणों में इसे अपने संभावित स्तर के बाहरी नियंत्रण को सक्षम करने के लिए चौथे लीड के रूप में समाप्त किया जाता है।

स्रोत और ड्रेन टर्मिनलों को आमतौर पर एन-डोपेड क्षेत्रों में धातु के संपर्कों का उपयोग करके जोड़ा जाता है।

हालांकि, यह कल्पना करना महत्वपूर्ण हो सकता है कि अंजीर में 5.31 दो n-doped क्षेत्रों के बीच का चैनल गायब है।

यह एक कमी-प्रकार और एक वृद्धि-प्रकार MOSFET के आंतरिक लेआउट के बीच मौलिक असमानता के रूप में माना जा सकता है, यह एक अंतर्निहित चैनल की अनुपस्थिति है जो डिवाइस का एक हिस्सा माना जाता है।

SiO2 परत को अभी भी प्रचलित देखा जा सकता है, जो गेट टर्मिनल के धातु आधार और नाली और स्रोत के बीच के क्षेत्र के बीच अलगाव सुनिश्चित करता है। हालांकि, यहां इसे पी-टाइप सामग्री अनुभाग से अलग खड़े देखा जा सकता है।

उपरोक्त चर्चा से हम यह निष्कर्ष निकाल सकते हैं कि MOSFET के एन्हांसमेंट प्रकार के लिए नाली / स्रोत के बीच अनुपलब्ध चैनल को छोड़कर, एक घटती और वृद्धि MOSFET आंतरिक लेआउट में कुछ समानताएँ हो सकती हैं।

मूल संचालन और विशेषताएँ

एन्हांसमेंट प्रकार MOSFET के लिए, जब 0 V अपने VGS में पेश किया जाता है, तो लापता n-चैनल (जो कि बहुत सारे मुफ्त वाहक ले जाने के लिए जाना जाता है) के कारण एक वर्तमान आउटपुट शून्य हो जाता है, जो कि एक ख़राब प्रकार के विपरीत है MOSFET का, ID = IDSS का होना।

ऐसी स्थिति में नाली / स्रोत टर्मिनलों के बीच एक अनुपलब्ध पथ के कारण, इलेक्ट्रॉनों के रूप में बड़ी मात्रा में वाहक नाली / स्रोत (एन-डोपेड क्षेत्रों के कारण) पर जमा नहीं हो पाते हैं।

वीडीएस में कुछ सकारात्मक क्षमता को लागू करते हुए, वीजीएस के साथ शून्य वोल्ट पर सेट और एसएस टर्मिनल स्रोत टर्मिनल के साथ छोटा है, हम वास्तव में एन-डोपेड क्षेत्रों और पी-सब्सट्रेट के बीच रिवर्स पक्षपाती जंक्शन जंक्शनों के एक जोड़े को किसी भी उल्लेखनीय चालन को सक्षम करने के लिए पाते हैं। स्रोत के लिए नाली।

अंजीर में 5.32 एक ऐसी स्थिति को दर्शाता है जिसमें VDS और VGS को 0 V से अधिक कुछ सकारात्मक वोल्टेज के साथ लागू किया जाता है, जिससे स्रोत के संबंध में नाली और गेट को सकारात्मक क्षमता पर रखा जा सकता है।

गेट पर सकारात्मक क्षमता SiO2 परत के किनारे के साथ पी-सब्सट्रेट में छेद को धक्का देती है जो स्थान को छोड़ती है और पी-सब्सट्रेट के क्षेत्रों में गहराई से प्रवेश करती है, जैसा कि उपरोक्त आंकड़े में दिखाया गया है। ऐसा एक जैसे आरोपों के कारण होता है जो एक दूसरे को दोहराते हैं।

इसका परिणाम यह होता है कि कमी वाले क्षेत्र को SiO2 इन्सुलेट परत के करीब बनाया जाता है जो छिद्रों से रहित होता है।

इसके बावजूद, पी-सब्सट्रेट इलेक्ट्रॉनों जो सामग्री के अल्पसंख्यक वाहक हैं, सकारात्मक द्वार की ओर खींचे जाते हैं और SiO2 परत की सतह के करीब के क्षेत्र में इकट्ठा होने लगते हैं।

SiO2 परत नकारात्मक वाहकों की इन्सुलेशन संपत्ति के कारण नकारात्मक वाहक को गेट टर्मिनल पर अवशोषित होने की अनुमति देता है।

जैसा कि हम VGS के स्तर को बढ़ाते हैं, SiO2 सतह के करीब इलेक्ट्रॉन घनत्व भी बढ़ता है, जब तक कि अंत में प्रेरित एन-प्रकार क्षेत्र नाली / स्रोत में एक मात्रात्मक चालन की अनुमति देने में सक्षम होता है।

VGS परिमाण जो नाली की धारा में एक इष्टतम वृद्धि का कारण बनता है, को दहलीज वोल्टेज कहा जाता है, प्रतीक वीटी द्वारा हस्ताक्षरित । डेटाशीट्स में आप इसे VGS (Th) के रूप में देख पाएंगे।

जैसा कि ऊपर सीखा गया है, VGS = 0 पर एक चैनल की अनुपस्थिति के कारण, और सकारात्मक गेट-टू-सोर्स वोल्टेज एप्लिकेशन के साथ 'बढ़ाया', इस प्रकार के MOSFET को एन्हांसमेंट-प्रकार MOSFETs के रूप में जाना जाता है।

आप पाएंगे कि दोनों कमी- और वृद्धि-प्रकार MOSFETs वृद्धि-प्रकार क्षेत्रों को प्रदर्शित करते हैं, लेकिन शब्द वृद्धि उत्तरार्द्ध के लिए उपयोग किया जाता है क्योंकि यह विशेष रूप से ऑपरेशन के एन्हांसमेंट मोड का उपयोग करके काम करता है।

अब, जब वीजीएस को थ्रेशोल्ड मान से अधिक धकेल दिया जाता है, तो फ्री कैरियर्स की एकाग्रता उस चैनल में बढ़ावा देगी जहां यह प्रेरित है। इससे नाली का करंट बढ़ जाता है।

दूसरी ओर, यदि हम VGS को स्थिर रखते हैं और VDS (ड्रेन-टू-सोर्स वोल्टेज) के स्तर को बढ़ाते हैं, तो इससे MOSFET अपने संतृप्ति बिंदु तक पहुंच जाएगा, जैसा कि आम तौर पर किसी भी JFET या एक विघटन MOSFET के साथ भी होता है।

जैसा कि अंजीर में दिखाया गया है। 5.33 में ड्रेन करंट आईडी को पिंचिंग-ऑफ प्रक्रिया की सहायता से समतल किया जाता है, जो संकरे चैनल द्वारा प्रेरित चैनल के ड्रेन एंड की ओर इंगित करता है।

किफ़ॉफ़ के वोल्टेज कानून को MOSFET के टर्मिनल वॉल्यूम में अंजीर में 5.33 पर लागू करके, हम प्राप्त करते हैं:

यदि VGS को एक विशिष्ट मान के लिए स्थिर रखा जाता है, उदाहरण के लिए 8 V, और VDS 2 से 5 V, वोल्टेज VDG Eq द्वारा उठाया जाता है। 5.11 को -6 से -3 वी तक गिरते हुए देखा जा सकता है, और गेट की क्षमता कम वोल्टेज के संबंध में कम और कम सकारात्मक हो रही है।

यह प्रतिक्रिया मुक्त वाहकों या इलेक्ट्रॉनों को प्रेरित चैनल के इस क्षेत्र की ओर खींचने से रोकती है, जिसके परिणामस्वरूप चैनल की प्रभावी चौड़ाई में गिरावट आती है।

अंत में, चैनल की चौड़ाई चुटकी बंद के बिंदु तक कम हो जाती है, जो पहले से ही हमारे पहले के कमी MOSFET लेख में हमने सीखा है के समान एक संतृप्ति स्थिति तक पहुंच गई है।

मतलब, एक निश्चित वीजीएस के साथ वीडीएस को और अधिक बढ़ाना आईडी के संतृप्ति स्तर को प्रभावित नहीं करता है, जब तक कि उस बिंदु पर जहां एक टूटने की स्थिति नहीं पहुंचती है।

अंजीर 5.34 को देखते हुए हम पहचान सकते हैं कि MOSFET के लिए Fig.5.33 में VGS = 8 V होने के कारण, संतृप्ति 6 V के VDS स्तर पर होती है। सटीक होने के लिए VDS संतृप्ति स्तर लागू किए गए GGS स्तर से जुड़ा होता है:

इसमें कोई संदेह नहीं है, इसका मतलब यह है कि जब वीटी मूल्य तय हो जाता है, तो वीजीएस के स्तर में वृद्धि करने से आनुपातिक स्तर पर संतृप्ति स्तर के नियंत्रण के माध्यम से वीडीएस के लिए संतृप्ति के उच्च स्तर का कारण होगा।

उपरोक्त आंकड़े में दिखाई गई विशेषताओं का उल्लेख करते हुए, वीटी स्तर 2 वी है, जो इस तथ्य से स्पष्ट है कि नाली का वर्तमान 0 एमए तक गिर गया है।

इसलिए आमतौर पर हम कह सकते हैं:

जब VGS मान वृद्धि-प्रकार MOSFET के लिए सीमा स्तर से कम होता है, तो इसकी नाली वर्तमान 0 mA होती है।

हम उपरोक्त आंकड़े में भी स्पष्ट रूप से देख सकते हैं कि जब तक वीजीएस को वीटी से 8 वी तक ऊपर उठाया जाता है, आईडी के लिए इसी संतृप्ति स्तर भी 0 से 10 एमए स्तर तक बढ़ जाता है।

इसके अलावा हम आगे यह नोटिस कर सकते हैं कि VGS के स्तर के बीच का स्थान VGS के मूल्य में वृद्धि के साथ बढ़ता है, जिससे नाली के प्रवाह में एक असीम रूप से वृद्धि होती है।

हम पाते हैं कि ड्रेन करंट वैल्यू वीजीएस स्तर के लिए गेट-टू-सोर्स वोल्टेज से संबंधित है जो वीटी से अधिक है, निम्नलिखित गैर-रिलेशनशिप संबंधों के माध्यम से:

जो शब्द स्क्वर्ट ब्रैकेट में दिखाया गया है, वह शब्द वह है जो आईडी और वीजीएस के बीच नॉनलाइनियर रिलेटिंशशिप के लिए जिम्मेदार है।

शब्द k एक स्थिर है और MOSFET लेआउट का एक कार्य है।

हम निम्न समीकरण के माध्यम से इस निरंतर k का मान ज्ञात कर सकते हैं:

जहां आईडी (पर) और वीजीडी (पर) प्रत्येक विशेष रूप से डिवाइस की विशेषता के आधार पर मूल्य हैं।

अगले अंजीर में 5.35 नीचे हम पाते हैं कि एक दूसरे के बीच स्थानांतरण प्रक्रिया को स्पष्ट करने के लिए नाली और हस्तांतरण विशेषताओं को एक दूसरे के बगल में व्यवस्थित किया गया है।

मूल रूप से, यह JFET और कमी-प्रकार MOSFETs के लिए पहले बताई गई प्रक्रिया के समान है।

हालांकि, वर्तमान मामले के लिए हमें यह याद रखना होगा कि वीजीएस वीटी के लिए ड्रेन करंट 0 mA है।

यहां ID में करंट की मात्रा देखी जा सकती है, जो Eq द्वारा निर्धारित की गई वृद्धि होगी। 5.13।

ध्यान दें, नाली विशेषताओं से स्थानांतरण विशेषताओं पर बिंदुओं को परिभाषित करते हुए, हम केवल संतृप्ति स्तरों पर विचार करते हैं। यह EDS द्वारा स्थापित संतृप्ति स्तरों की तुलना में VDS मानों के संचालन के क्षेत्र को प्रतिबंधित करता है। (5.12) है।

पी-चैनल एन्हांसमेंट-टाइप MOSFETs

एक पी-चैनल एन्हांसमेंट-टाइप MOSFET की संरचना जैसा कि अंजीर में दिखाया गया है। 5.37a अंजीर में प्रदर्शित होने के ठीक विपरीत है।

मतलब, अब आप पाते हैं कि नाली और स्रोत जोड़ों के नीचे एक एन-प्रकार सब्सट्रेट और पी-डॉप्ड क्षेत्र।

टर्मिनलों की स्थापना जारी है, लेकिन वर्तमान दिशाओं और वोल्टेज ध्रुवीयता में से प्रत्येक उलट है।

वीजीएस के लगातार अधिक नकारात्मक परिमाण के कारण करंट की बढ़ती मात्रा के कारण, नाली की विशेषताएं अंजीर में दी गई हैं।

अंतरण विशेषताएँ अंजीर 5.35 के अंतरण वक्र के आई डी इंप्रेशन (आईडी अक्ष के आसपास) होगी, जो वीटी के ऊपर वीजीएस के अधिक से अधिक नकारात्मक मूल्यों के साथ बढ़ती हुई है, जैसा कि अंजीर में प्रदर्शित किया गया है। समीकरण (5.11) के माध्यम से (5.14) पी-चैनल उपकरणों के लिए समान रूप से उपयुक्त हैं।

संदर्भ:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

पिछला: एंटी जासूस आरएफ डिटेक्टर सर्किट - वायरलेस बग डिटेक्टर अगला: स्थानांतरण विशेषताओं