ECL (एमिटर कपल्ड लॉजिक) का आविष्कार पहली बार IBM में अगस्त 1956 में Hannon S. Yourke द्वारा किया गया था। इस लॉजिक को करंट मोड लॉजिक के रूप में भी जाना जाता है, जिसका उपयोग आईबीएम 7090 और 7094 के कंप्यूटरों में किया जाता है। ईसीएल परिवार की तुलना में बहुत तेज है। डिजिटल तर्क परिवार। आम तौर पर, यह तर्क परिवार 1 एनएस से कम का प्रसार विलंब प्रदान करता है। यह बाइपोलर जंक्शन ट्रांजिस्टर पर आधारित एक तार्किक परिवार है। यह सबसे तेज़ लॉजिक फ़ैमिली सर्किट है जो पारंपरिक लॉजिक सिस्टम को डिज़ाइन करने के लिए सुलभ है। यह लेख एक के सिंहावलोकन पर चर्चा करता है एमिटर युग्मित तर्क-सर्किट , अनुप्रयोगों के साथ काम करना।

एमिटर युग्मित तर्क क्या है?

एमिटर-युग्मित तर्क सबसे अच्छा है बीजेटी -आधारित तर्क परिवार पारंपरिक तर्क-प्रणाली डिजाइन में उपयोग किया जाता है। कभी-कभी, इसे करंट मोड लॉजिक भी कहा जाता है जो एक बहुत ही उच्च गति वाली डिजिटल तकनीक है। आम तौर पर, ECL को सबसे तेज़ लॉजिक IC माना जाता है जहाँ यह बहुत छोटे वोल्टेज स्विंग का उपयोग करके अपने उच्च गति के संचालन को प्राप्त करता है और ट्रांजिस्टर को संतृप्ति क्षेत्र में प्रवेश करने से भी रोकता है।

ईसीएल का कार्यान्वयन एक सकारात्मक आपूर्ति वोल्टेज का उपयोग करता है जिसे पीईसीएल या सकारात्मक-संदर्भित ईसीएल के रूप में जाना जाता है। प्रारंभिक ईसीएल फाटकों में, शोर प्रतिरक्षा के कारण एक नकारात्मक वोल्टेज आपूर्ति का उपयोग किया जाता है। उसके बाद, सकारात्मक-संदर्भित ईसीएल टीटीएल तर्क परिवारों की तुलना में अपने अधिक संगत तर्क स्तरों के कारण बहुत प्रसिद्ध हो गया।

एमिटर-युग्मित तर्क स्थिर शक्ति की एक बड़ी मात्रा को नष्ट कर देता है, हालांकि, इसकी कुल खपत वर्तमान की तुलना में कम है सीएमओएस उच्च आवृत्तियों पर। इसलिए, ईसीएल मुख्य रूप से घड़ी-वितरण सर्किट और उच्च आवृत्ति-आधारित अनुप्रयोगों में फायदेमंद है।

एमिटर युग्मित तर्क विशेषताएं

ईसीएल की विशेषताएं उन्हें कई उच्च-प्रदर्शन-आधारित अनुप्रयोगों में उपयोग करेंगी।

- ईसीएल दो आउटपुट प्रदान करता है जो हमेशा एक दूसरे के पूरक होते हैं क्योंकि सर्किट का संचालन एक अंतर एम्पलीफायर पर आधारित होता है।

- यह तर्क परिवार मुख्य रूप से अखंड निर्माण विधियों के लिए उपयुक्त है क्योंकि तर्क स्तर प्रतिरोधक अनुपात का एक कार्य है।

- ईसीएल परिवार के उपकरण किसी बाहरी इनवर्टर का उपयोग किए बिना प्रस्तावित फ़ंक्शन का सही और पूरक आउटपुट उत्पन्न करते हैं। नतीजतन, यह पैकेज की संख्या और बिजली की आवश्यकताओं को कम करता है और समय की देरी से होने वाली समस्याओं को भी कम करता है।

- डिफरेंशियल एम्पलीफायर डिज़ाइन में ECL डिवाइस व्यापक प्रदर्शन लचीलापन प्रदान करते हैं, इसलिए ECL सर्किट डिजिटल और लीनियर सर्किट दोनों के रूप में उपयोग करने की अनुमति देते हैं।

- ईसीएल गेट के डिजाइन में सामान्य रूप से उच्च और निम्न इनपुट प्रतिबाधा होती है, जो बड़े फैन-आउट के साथ-साथ ड्राइव क्षमता प्राप्त करने के लिए बेहद अनुकूल है।

- ईसीएल उपकरण बिजली आपूर्ति के डिजाइन को सरल बनाने के लिए बिजली की आपूर्ति पर एक निरंतर वर्तमान नाली उत्पन्न करते हैं।

- खुले एमिटर आउटपुट सहित ईसीएल के उपकरण बस उन्हें ट्रांसमिशन लाइन ड्राइव क्षमता को शामिल करने की अनुमति देते हैं।

एमिटर युग्मित तर्क सर्किट

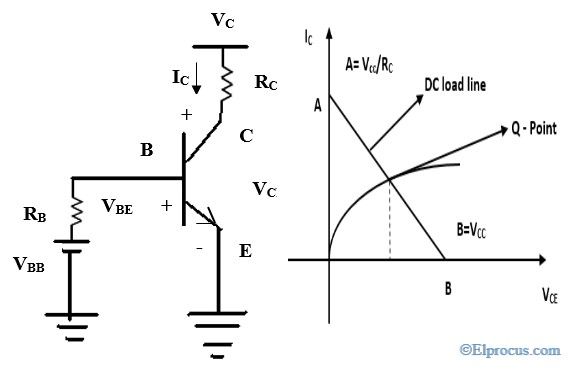

इन्वर्टर के लिए एमिटर-कपल्ड लॉजिक सर्किट नीचे दिखाया गया है जिसे रेसिस्टर्स और ट्रांजिस्टर के साथ डिज़ाइन किया गया है। इस सर्किट में, दो ट्रांजिस्टर के एमिटर टर्मिनलों को केवल वर्तमान सीमित प्रतिरोध आरई से जोड़ा जाता है जिसका उपयोग ट्रांजिस्टर को संतृप्ति में प्रवेश करने से रोकने के लिए किया जाता है। यहां ट्रांजिस्टर का आउटपुट एमिटर टर्मिनल के बजाय कलेक्टर टर्मिनल से लिया जाता है। यह सर्किट दो आउटपुट वाउट (इनवर्टिंग आउटपुट) और वाउट 2 (नॉन-इनवर्टिंग आउटपुट) और विन जैसे इनपुट टर्मिनल प्रदान करता है जहां उच्च या निम्न इनपुट दिया जाता है। + वीसीसी = 5 वी।

एमिटर युग्मित तर्क कैसे काम करता है?

एमिटर-कपल्ड लॉजिक का संचालन यह है कि जब भी ECL सर्किट को हाई इनपुट दिया जाता है, तो यह 'Q1' ट्रांजिस्टर को ON और Q2 ट्रांजिस्टर को बंद कर देगा लेकिन Q1 ट्रांजिस्टर संतृप्त नहीं होता है। तो यह VOUT2 आउटपुट को उच्च तक खींच लेगा और R1 के भीतर गिरावट के कारण VOUT1 आउटपुट का मान कम होगा।

इसी तरह, जब ECL को दिया गया VIN मान LOW होता है, तो यह Q1 ट्रांजिस्टर को OFF और Q2 ट्रांजिस्टर को ON कर देगा। तो, Q2 ट्रांजिस्टर संतृप्ति में नहीं जाएगा। तो यह VOUT1 आउटपुट को उच्च मान खींचेगा और R2 प्रतिरोध के भीतर गिरावट के कारण VOUT2 आउटपुट मान कम होगा।

आइए देखें कि वोल्टेज लागू होने पर ट्रांजिस्टर Q1 और Q2 कैसे चालू और बंद होते हैं।

इस सर्किट में Q1 और Q2 जैसे दो ट्रांजिस्टर एक आम एमिटर रेसिस्टर द्वारा डिफरेंशियल एम्पलीफायर के रूप में जुड़े हुए हैं।

इस उदाहरण सर्किट के लिए वोल्टेज आपूर्ति वीसीसी = 5.0, वीबीबी = 4.0 और वीईई = 0 वी है। इनपुट हाई और लो-लेवल वैल्यू को केवल 4.4 वी और 3.6 वी के रूप में परिभाषित किया गया है। दरअसल, यह सर्किट कम आउटपुट और उच्च स्तर उत्पन्न करता है जो 0.6 वोल्ट अधिक होता है; हालाँकि, इसे वास्तविक ECL सर्किट में ठीक किया जाता है।

एक बार जब विन हाई हो जाता है, तो Q1 ट्रांजिस्टर चालू हो जाता है, हालांकि संतृप्त नहीं होता है और Q2 ट्रांजिस्टर बंद हो जाता है। तो, VOUT2 जैसे आउटपुट वोल्टेज को R2 रोकनेवाला के माध्यम से 5 V तक खींचा जाता है और यह दिखाया जा सकता है कि R1 रोकनेवाला के पार वोल्टेज ड्रॉप लगभग 0.8 V है ताकि VOUT1 = 4.2 V (LOW)। इसके अलावा VE = VOUT1 - VQ1 => 4.2V - 0.4V = 3.8V क्योंकि ट्रांजिस्टर Q1 पूरी तरह से चालू है।

एक बार जब विन कम हो जाता है, तो Q2 ट्रांजिस्टर चालू हो जाएगा, लेकिन संतृप्त नहीं होगा और Q1 ट्रांजिस्टर बंद हो जाएगा। इसलिए, VOUT1 को R1 रोकनेवाला का उपयोग करके 5.0 V तक खींचा जाता है और यह दिखाया जा सकता है कि VOUT2 4.2 V है। साथ ही VE => VOUT2 - VQ2 => 4.2V - 0.8V => 3.4V क्योंकि ट्रांजिस्टर Q2 चालू है।

ECL में, दो ट्रांजिस्टर कभी भी संतृप्ति में नहीं होते हैं क्योंकि t वह इनपुट / आउटपुट वोल्टेज स्विंग 0.8v . की तरह काफी छोटा है और इनपुट प्रतिबाधा अधिक है और आउटपुट प्रतिरोध कम है। यह ईसीएल को कम प्रसार विलंब समय के साथ तेजी से संचालित करने में मदद करता है।

दो इनपुट एमिटर युग्मित तर्क या/NOR गेट सर्किट

दो इनपुट एमिटर युग्मित तर्क OR/NOR गेट सर्किट नीचे दिखाया गया है। यह सर्किट उपरोक्त इन्वर्टर सर्किट को संशोधित करके बनाया गया है। संशोधन इनपुट पक्ष में एक अतिरिक्त ट्रांजिस्टर जोड़कर है।

इस सर्किट का कार्य बहुत सरल है। जब Q1 और Q2 दोनों ट्रांजिस्टर पर लागू इनपुट कम होते हैं तो आउटपुट 1 (Vout1) को उच्च मान पर बना देगा। तो, यह Vout1NOR गेट के आउटपुट के अनुरूप है।

इसके साथ ही, यदि Q3 ट्रांजिस्टर को चालू किया जाता है, तो यह दूसरे आउटपुट (Vout2) को उच्च बना देगा। तो, यह Vou2 आउटपुट OR गेट आउटपुट से मेल खाता है।

उसी तरह, यदि दोनों Q1 और Q2 ट्रांजिस्टर इनपुट उच्च हैं, तो यह Q1 और Q2 ट्रांजिस्टर को चालू करेगा और VOUT1 टर्मिनल पर कम आउटपुट प्रदान करेगा।

यदि इस पूरे ऑपरेशन के दौरान Q3 ट्रांजिस्टर को बंद कर दिया जाता है तो यह VOUT2 टर्मिनल पर उच्च आउटपुट प्रदान करेगा। तो, OR/NOR गेट के लिए सत्य तालिका नीचे दी गई है।

|

इनपुट |

इनपुट | या |

न |

|

ए |

बी | यू | यू |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

एमिटर-युग्मित तर्क विशेषताएँ

ईसीएल की विशेषताओं में निम्नलिखित शामिल हैं।

- टीटीएल की तुलना में, ईसीएल का तेजी से प्रसार समय 0.5 से 2 एनएस तक है। लेकिन, एमिटर युग्मित तर्क शक्ति अपव्यय टीटीएल की तुलना में 30 मेगावाट की तुलना में अधिक है।

- ECL के I/O वोल्टेज में 0.8 जैसा छोटा स्विंग होता है।

- ईसीएल का इनपुट प्रतिबाधा अधिक है और आउटपुट प्रतिरोध कम है; नतीजतन, ट्रांजिस्टर अपनी अवस्थाओं को बहुत तेजी से बदलता है।

- ईसीएल की फैन-आउट क्षमता अधिक है और गेट विलंब कम है।

- ECL का o/p तर्क निम्न से उच्च अवस्था में बदल जाता है लेकिन इन राज्यों के लिए वोल्टेज का स्तर TTL और EC के बीच भिन्न होगा।

- ईसीएल की शोर प्रतिरक्षा 0.4V है।

फायदे और नुकसान

एमिटर-युग्मित तर्क के लाभ नीचे चर्चा की गई है।

- ईसीएल का फैनआउट 25 है जो टीटीएल की तुलना में बेहतर है और सीएमओएस की तुलना में यह कम है।

- ईसीएल का औसत प्रसार विलंब समय 1 से 4 एनएस है जो सीएमओएस और दोनों की तुलना में बेहतर है।

- टीटीएल। इस प्रकार इसे सबसे तेज तर्क परिवार कहा जाता है।

- जब एमिटर युग्मित में BJTs तर्क द्वार सक्रिय क्षेत्र में काम करते हैं, तो उनके पास सभी तर्क परिवारों की तुलना में अधिकतम गति होती है।

- ईसीएल गेट पूरक आउटपुट उत्पन्न करते हैं।

- बिजली आपूर्ति लीड में करंट स्विचिंग स्पाइक्स नहीं होते हैं।

- वायर्ड-या फ़ंक्शन प्रदान करने के लिए आउटपुट को संयुक्त रूप से जोड़ा जा सकता है।

- ईसीएल के पैरामीटर तापमान के माध्यम से ज्यादा नहीं बदलते हैं।

- नहीं। केवल चिप से सुलभ कार्यों की संख्या अधिक है।

एमिटर-युग्मित तर्क के नुकसान नीचे चर्चा की गई है।

- इसमें बेहद कम शोर मार्जिन यानी ±200 एमवी है।

- अन्य लॉजिक गेट्स की तुलना में बिजली अपव्यय अधिक है।

- अन्य तर्क परिवारों के साथ इंटरफेस करने के लिए, स्तर के शिफ्टर्स आवश्यक हैं।

- फैनआउट कैपेसिटिव लोडिंग को सीमित करता है।

- इसकी तुलना में टीटीएल ईसीएल गेट महंगे हैं।

- सीएमओएस और टीटीएल की तुलना में, ईसीएल शोर प्रतिरक्षा सबसे खराब है।

अनुप्रयोग

एमिटर-युग्मित तर्क के अनुप्रयोगों में निम्नलिखित शामिल हैं।

- एमिटर-कपल्ड लॉजिक का उपयोग फाइबर-ऑप्टिक ट्रांसीवर इंटरफेस, ईथरनेट और एटीएम (एसिंक्रोनस ट्रांसफर मोड) नेटवर्क जैसे अत्यंत उच्च गति संचार उपकरणों के भीतर एक तर्क और इंटरफ़ेस तकनीक के रूप में किया जाता है।

- ईसीएल बीजेटी पर आधारित एक तार्किक परिवार है जहां अपेक्षाकृत छोटे वोल्टेज स्विंग का उपयोग करके और ट्रांजिस्टर को संतृप्ति क्षेत्र में जाने से बचाकर इसका उच्च गति संचालन प्राप्त किया जा सकता है।

- ईसीएल का उपयोग आईबीएम 360/91 के भीतर एएसएलटी सर्किट बनाने में किया जाता है।

- ECL एक इन्वर्टर फ़ंक्शन प्राप्त करने के लिए प्राथमिक और द्वितीयक ट्रांजिस्टर के बीच सिंगल-एंडेड बायस i/p और सकारात्मक प्रतिक्रिया का उपयोग करके स्टैक्ड ट्रांजिस्टर के उपयोग से बचा जाता है।

- ECL का उपयोग अत्यंत उच्च गति वाले इलेक्ट्रॉनिक्स में किया जाता है।

इस प्रकार, यह है एमिटर युग्मित तर्क का अवलोकन या ईसीएल - सर्किट, कार्य, सुविधाएँ, विशेषताएँ, और अनुप्रयोग। अन्य डिजिटल लॉजिक परिवारों की तुलना में ECL BJT पर आधारित सबसे तेज़ लॉजिक फ़ैमिली है। यह एक छोटे वोल्टेज स्विंग का उपयोग करके और ट्रांजिस्टर को संतृप्ति क्षेत्र में जाने से बचाकर अपनी अधिकतम गति संचालन प्राप्त करता है। यह तर्क परिवार अविश्वसनीय 1ns प्रसार विलंब प्रदान करता है और नवीनतम ECL परिवारों में, यह देरी कम हो जाती है। यहाँ आपके लिए एक प्रश्न है, ECL का वैकल्पिक नाम क्या है?