विभिन्न प्रकार के डिजिटल सिस्टम का निर्माण बहुत ही प्रकार के बुनियादी नेटवर्क विन्यासों जैसे कि AND गेट, NAND गेट, या गेट आदि से किया जाता है। इन प्राथमिक सर्किट का उपयोग विभिन्न टोपोलॉजिकल कॉम्बिनेशन में बार-बार किया जाता है। लॉजिक प्रदर्शन करने के अलावा, डिजिटल सिस्टम को बाइनरी नंबर भी स्टोर करना होगा। इन मेमोरी सेल्स के लिए भी जाना जाता है फ्लिप फ्लॉप' s डिजाइन किए हैं। बाइनरी जोड़ जैसे कुछ कार्य करने के लिए। इसलिए, इस तरह के कार्य करने के लिए, के संयोजन तर्क द्वार और FLIP-FLOPs एक सिंगल-चिप IC पर डिज़ाइन किए गए हैं। ये IC डिजिटल सिस्टम के व्यावहारिक बिल्डिंग ब्लॉक्स हैं। बाइनरी जोड़ के लिए इस्तेमाल किए जाने वाले ऐसे बिल्डिंग ब्लॉक्स में से एक है कैरी लुक-फॉरवर्ड अडर।

कैरी लुक-फॉरवर्ड अडर क्या है?

एक डिजिटल कंप्यूटर में सर्किट शामिल होने चाहिए जो अंकगणित संचालन जैसे जोड़, घटाव, गुणा और भाग कर सकते हैं। इनमें, जोड़ और घटाव मूल संचालन हैं जबकि गुणा और भाग क्रमशः दोहराया जोड़ और घटाव हैं।

इन ऑपरेशनों को करने के लिए 'अडर सर्किट' को बुनियादी लॉजिक गेट्स का उपयोग करके लागू किया जाता है। योजक सर्किट हाफ-योजक, पूर्ण-योजक, रिपल-कैरी अडर, और कैरी लुक-आगे योजक के रूप में विकसित हुए हैं।

इन कैरी लुक-फॉरवर्ड अडर में तेजी से जोड़ने वाला सर्किट है। यह अधिक जटिल हार्डवेयर सर्किटरी का उपयोग करके, प्रसार देरी को कम करता है, जो इसके अलावा होता है। इसे रिपल-कैरी अडर सर्किट में परिवर्तित करके डिज़ाइन किया गया है ताकि योजक का कैरी लॉजिक दो-स्तरीय लॉजिक में बदल जाए।

4-बिट कैरी लुक-फॉरवर्ड अडर

समानांतर योजक में, प्रत्येक पूर्ण योजक के कैरी आउटपुट को अगले उच्च-क्रम राज्य में ले जाने वाले इनपुट के रूप में दिया जाता है। इसलिए, ये योजक किसी भी राज्य के कैरी और आउटपुट का उत्पादन करना संभव नहीं है जब तक कि उस राज्य के लिए कैरी इनपुट उपलब्ध न हो।

इसलिए, गणना होने के लिए, सर्किट को सभी राज्यों तक ले जाने के लिए प्रचारित होने तक इंतजार करना पड़ता है। यह सर्किट में प्रसार की देरी को प्रेरित करता है।

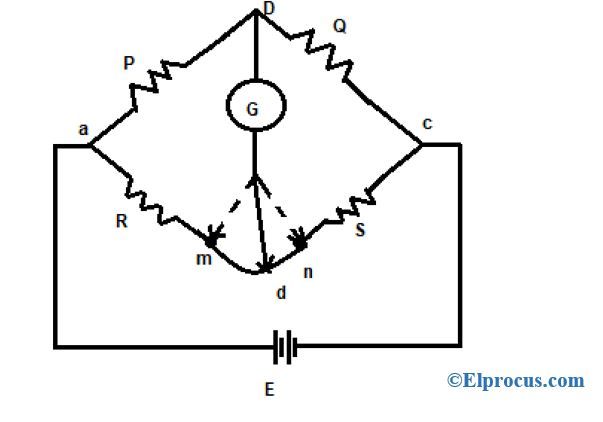

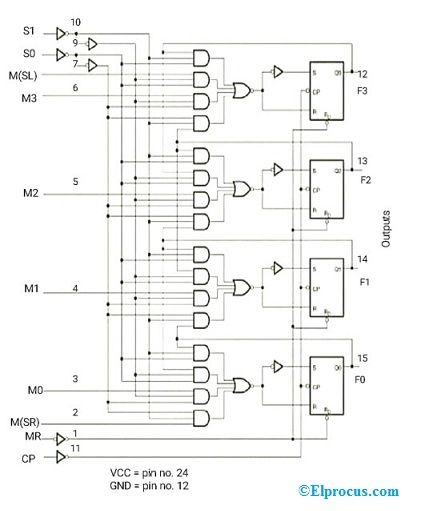

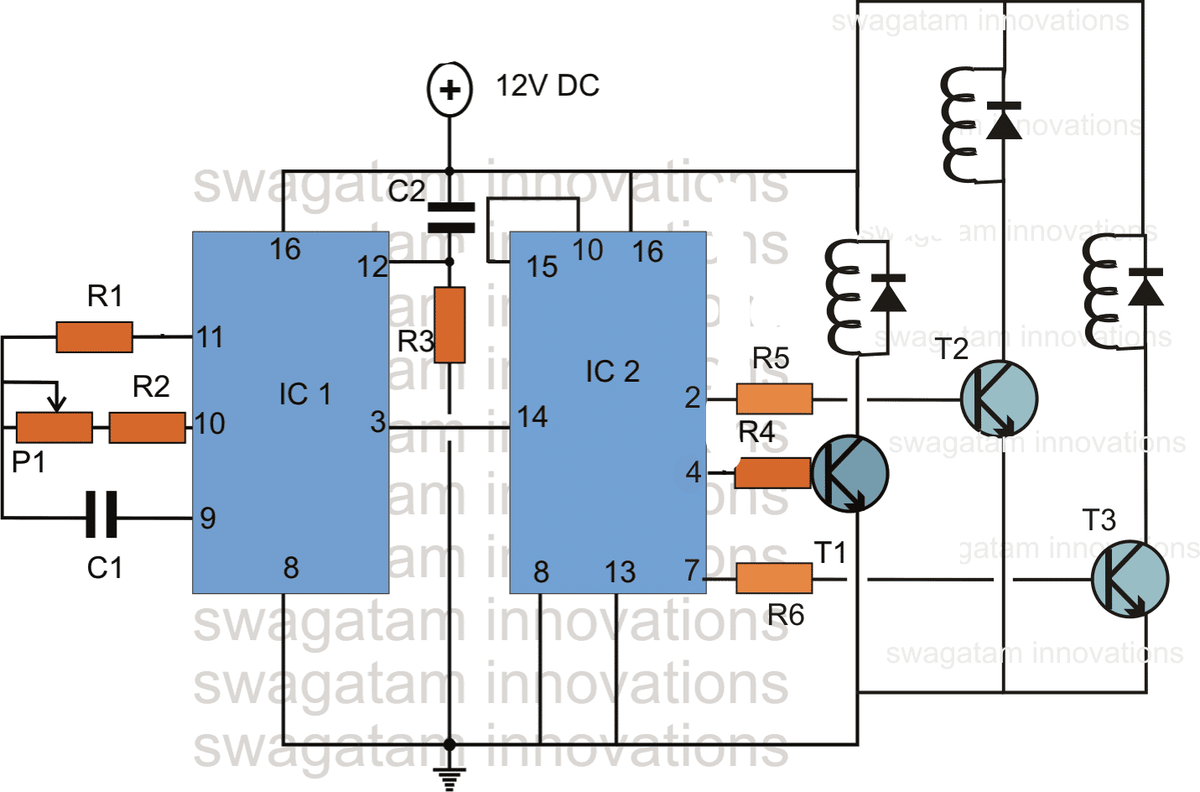

4-बिट-रिपल-कैरी-एडडर

ऊपर 4-बिट रिपल कैरी योजक सर्किट पर विचार करें। यहां S3 और B3 दिए जाने के साथ ही S3 का उत्पादन किया जा सकता है। लेकिन कैरी कै 3 की गणना तब तक नहीं की जा सकती है जब तक कि कैरी बिट C2 लागू न हो, जबकि C2 C1 पर निर्भर करता है। इसलिए अंतिम स्थिर-राज्य परिणामों का उत्पादन करने के लिए, सभी राज्यों के माध्यम से प्रचार प्रसार किया जाना चाहिए। यह सर्किट के कैरी प्रसार विलंब को बढ़ाता है।

योजक के प्रसार विलंब की गणना 'सर्किट में चरणों की संख्या के प्रत्येक गेट के प्रसार की देरी' के रूप में की जाती है। बड़ी संख्या में बिट्स की गणना के लिए, अधिक चरणों को जोड़ना पड़ता है, जो देरी को बहुत बदतर बना देता है। इसलिए, इस स्थिति को हल करने के लिए, कैरी लुक-फॉरवर्ड अडर पेश किया गया था।

कैरी लुक-फॉरवर्ड अडर की कार्यप्रणाली को समझने के लिए, 4-बिट कैरी लुक-फॉरवर्ड अडर नीचे वर्णित है।

4-बिट-कैरी-लुक-फॉरवर्ड-एडडर-लॉजिक-आरेख

इस योजक में, योजक के किसी भी स्तर पर कैरी इनपुट स्वतंत्र चरणों में उत्पन्न कैरी बिट्स से स्वतंत्र होता है। यहां किसी भी चरण का आउटपुट केवल उन बिट्स पर निर्भर करता है जो पिछले चरणों में जोड़े गए हैं और शुरुआती चरण में प्रदान किए गए इनपुट। इसलिए, किसी भी स्तर पर सर्किट को पिछले चरण से कैरी-बिट की पीढ़ी के लिए इंतजार नहीं करना पड़ता है और कैरी बिट का मूल्यांकन किसी भी समय किया जा सकता है।

ट्रुथ कैर्री लुक-फॉरवर्ड अडर

इस योजक की सत्य सारणी को प्राप्त करने के लिए, दो नए शब्द पेश किए गए हैं - कैरी जनरेट करना और प्रचार करना। जब भी कैरी जनरेट उत्पन्न होता है तो Gi + 1 कैरी करें। यह एआई और बीआई इनपुट पर निर्भर करता है। Gi 1 है, जब Ai और Bi दोनों 1 हैं। इसलिए, Gi की गणना Gi = Ai के रूप में की जाती है। द्वि।

कैरी प्रचारित पाई, सीआई से लेकर सि + 1 तक ले जाने के प्रचार से जुड़ा है। इसकी गणना Pi = Ai। Bi के रूप में की जाती है। इस योजक की सत्य तालिका को पूर्ण योजक की सत्य तालिका को संशोधित करने से प्राप्त किया जा सकता है।

Gi और Pi शब्दों का उपयोग करके Sum Si और Carry Ci + 1 नीचे दिए गए हैं -

- सि = पि = गी।

- Ci + 1 = Ci.Pi + Gi।

इसलिए, कैरी बिट्स C1, C2, C3 और C4 की गणना की जा सकती है

- C1 = C0.P0 + G0।

- C2 = C1.P1 + G1 = (C0.P0 + G0) .P1 + G1।

- C3 = C2.P2 + G2 = (C1.P1 + G1) .P2 + G2।

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3।

यह उन समीकरणों से देखा जा सकता है जो सि + 1 को ले जाते हैं, केवल कै 0 पर निर्भर करते हैं, मध्यवर्ती कैरी बिट्स पर नहीं।

कैरी-लुक-फ़ॉरवर्ड-अडर-ट्रुथ-टेबल

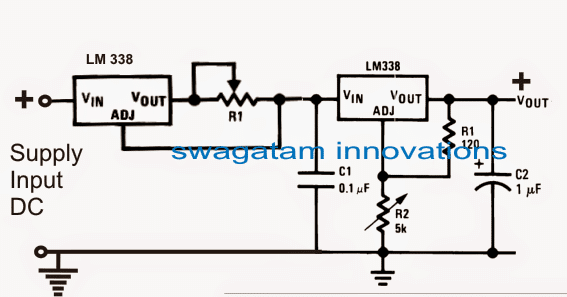

सर्किट आरेख

उपरोक्त समीकरणों को AND, OR गेट्स के साथ दो-स्तरीय कॉम्बिनेशन सर्किट का उपयोग करके कार्यान्वित किया जाता है, जहां गेटों को कई इनपुट माना जाता है।

कैरी-आउटपुट-जेनरेशन-सर्किट-ऑफ-कैरी-लुक-फॉर-अडर

कैर्री लुक-फॉरवर्ड अडर सर्किट में 4-बिट नीचे दिया गया है।

4-बिट-कैरी-लुक-फॉरवर्ड-एडडर-सर्किट-आरेख

8-बिट और 16-बिट कैरी लुक-फॉरवर्ड अडर सर्किट को कैरी लॉजिक के साथ 4-बिट योजक सर्किट को कैस्केडिंग करके डिज़ाइन किया जा सकता है।

कैरी लुक-फॉरवर्ड अडर के फायदे

इस योजक में, प्रसार देरी कम हो जाती है। किसी भी स्तर पर कैरी आउटपुट केवल प्रारंभिक चरण के शुरुआती कैरी बिट पर निर्भर है। इस योजक का उपयोग करके मध्यवर्ती परिणामों की गणना करना संभव है। यह योजक संगणना के लिए उपयोग किया जाने वाला सबसे तेज़ योजक है।

अनुप्रयोग

हाई-स्पीड कैरी लुक-फॉरवर्ड एडर्स को आईसी के रूप में लागू किया जाता है। इसलिए, योजक को सर्किट में एम्बेड करना आसान है। उच्च बिट बूलियन कार्यों के दो या अधिक योजक गणनाओं को आसानी से किया जा सकता है। यहां उच्चतर बिट्स के लिए उपयोग किए जाने पर फाटकों की संख्या में वृद्धि भी मध्यम है।

इस योजक के लिए क्षेत्र और गति के बीच एक व्यापार है। जब उच्च बिट गणना के लिए उपयोग किया जाता है, तो यह उच्च गति प्रदान करता है, लेकिन सर्किट की जटिलता भी बढ़ जाती है, जिससे सर्किट के कब्जे वाले क्षेत्र में वृद्धि होती है। यह योजक आमतौर पर 4-बिट मॉड्यूल के रूप में लागू किया जाता है जो उच्च गणना के लिए उपयोग किए जाने पर एक साथ कैस्केड किया जाता है। यह योजक अन्य योजक की तुलना में महंगा है।

कंप्यूटर में बूलियन संगणना के लिए, योजक नियमित रूप से उपयोग किए जा रहे हैं। चार्ल्स बैबेज ने कंप्यूटर में कैरी बिट की आशंका के लिए एक तंत्र लागू किया, जिससे होने वाली देरी को कम किया जा सके रिपल योजक जोड़ते हैं । एक प्रणाली को डिजाइन करते समय, गणना की गति एक डिजाइनर के लिए उच्चतम निर्णायक कारक है। 1957 में, गेराल्ड बी। रोसेनबर्गर ने आधुनिक बाइनरी कैरी लुक-फॉरवर्ड अडर का पेटेंट कराया। गेट की देरी और सिमुलेशन के विश्लेषण के आधार पर, इस योजक के सर्किट को संशोधित करने के लिए प्रयोगों को संचालित किया जा रहा है ताकि यह और भी तेज हो सके। एन-बिट कैरी लुक-फॉरवर्ड योजक के लिए, प्रत्येक गेट के 20 देरी होने पर प्रचार में देरी क्या है?

छवि क्रेडिट